# **FRED** easy

Semiautomatic defibrillator (PAD)

**Service Manual**

Version 01.00

# Revision history of the service manual

Version 01.00:

May 2003

### **WARNING**

This manual shall be considered to form an integral part of the device described.

This technical manual is intended for qualified personnel and describes the operating, maintenance and troubleshooting procedures for FRED EASY.

Compliance with its content is a prerequisite for proper device performance and for the safety of the patient and operator.

The manufacturer shall only be liable for the safety, reliability and performance of the device if:

- assembly, extensions, adjustments, modifications or repairs are performed by the manufacturer or by persons authorised by the manufacturer.

- the electrical installation of the facility of use complies with the requirements applicable in the country.

- the device is used in accordance with its instructions for use.

- the spare parts used are original parts from SCHILLER.

This manual describes the device at the time of printing.

The supply of this manual does not in any event constitute permission or approval to modify or repair a device.

The manufacturer agrees to supply all the spare parts for a period of ten years.

All rights reserved for the devices, circuits, processes and names appearing in this manual.

The FRED EASY device shall be used as described in the User's Manual. The device may not be used for any purpose that has not been specifically described in the manual, as such use could be hazardous.

# SAFETY INFORMATION

The product is marked as follows:

#### CE-0459

in accordance with the requirements of Council Directive 93/42/EEC relating to medical equipment, based on the essential requirements of annex I of the directive.

- It fully meets the electromagnetic compatibility requirements of standard IEC 60601-1-2/EN 60601-2 "Electromagnetic compatibility of medical electrical devices".

- The device has undergone interference suppression in accordance with the requirements of standard EN 50011, class B.

- In order to optimise patient safety, electromagnetic compatibility, accurate measurement indication and proper device performance, users are advised to use only original spare parts supplied by SCHILLER. Any use of accessories other than original accessories shall be at the exclusive risk of the user. The manufacturer shall not be liable for any damage due to the use of incompatible accessories or consumable supplies.

- The manufacturer shall only be liable for the safety, reliability and performance of the device if:

- assembly, configuration, modifications, extensions or repairs are made by personnel from SCHILLER MEDICAL or personnel duly authorised by SCHILLER MEDICAL.

- the device is used in accordance with its instructions for use.

- Any use of the device other than as described in the instructions for use shall be made at the

exclusive risk of the user.

- This manual covers the device version and the safety standards applicable at the time of printing. All rights reserved for the circuits, processes, names, software and devices appearing in this manual.

- The quality assurance system in use in the facilities of SCHILLER meets international standards EN ISO 9001 and EN 46001.

- Unless otherwise agreed in writing by SCHILLER, no part of the manufacturer's literature may be duplicated or reproduced.

# Safety symbols used on the device

Danger! High voltage

# **Conventions used in the manual**

| Danger: | indicates an imminent hazard which, if not avoided, will result in |

|---------|--------------------------------------------------------------------|

|         | death or serious injury to the user (and/or others).               |

|         |                                                                    |

| Caution: | Warning indicating conditions or actions that could lead to device |

|----------|--------------------------------------------------------------------|

|          | or software malfunctioning.                                        |

|          |                                                                    |

| Note: | Useful information for more effective and practical device operation.                |

|-------|--------------------------------------------------------------------------------------|

|       | Additional information or explanation relating to the paragraphs preceding the note. |

#### Manufacturer:

SCHILLER MEDICAL SA 4, rue Louis Pasteur ZAE sud F- 67 162 Wissembourg

Tel. : \*\*33 / (0) 3.88.63.36.00 Fax : \*\*33 / (0) 3.88.94.12.82

# PRECAUTIONS WHILE TESTING THE DEVICE

While testing the FRED EASY defibrillator, the patient may only be simulated with fixed high-voltage and high-power resistors that are well insulated from the ground or earth. Poorly insulated devices or devices with loose contacts or devices containing components such as spark arresters or electronic flash lamps may never be used as they could irremediably destroy the device.

# **CONTENTS**

| 1. ( | Operation                                                   | 1-1          |

|------|-------------------------------------------------------------|--------------|

| 1.1  | Display and controls                                        | 1-1          |

| 1.2  | Explanation of symbols used                                 | 1-2          |

| 1.3  | Device operation                                            | 1-3          |

|      | Defibrillation procedure                                    |              |

| 1.5  | Recording (optional)                                        | 1-6          |

|      | Technical specifications                                    |              |

| 2. T | Testing and maintenance                                     | 2-1          |

|      | Functional testing                                          |              |

|      | Systematic verification before use                          |              |

|      | Cleaning and disinfecting                                   |              |

|      | Froubleshooting                                             |              |

|      | Replacement of parts                                        |              |

|      | Device disassembly procedure                                |              |

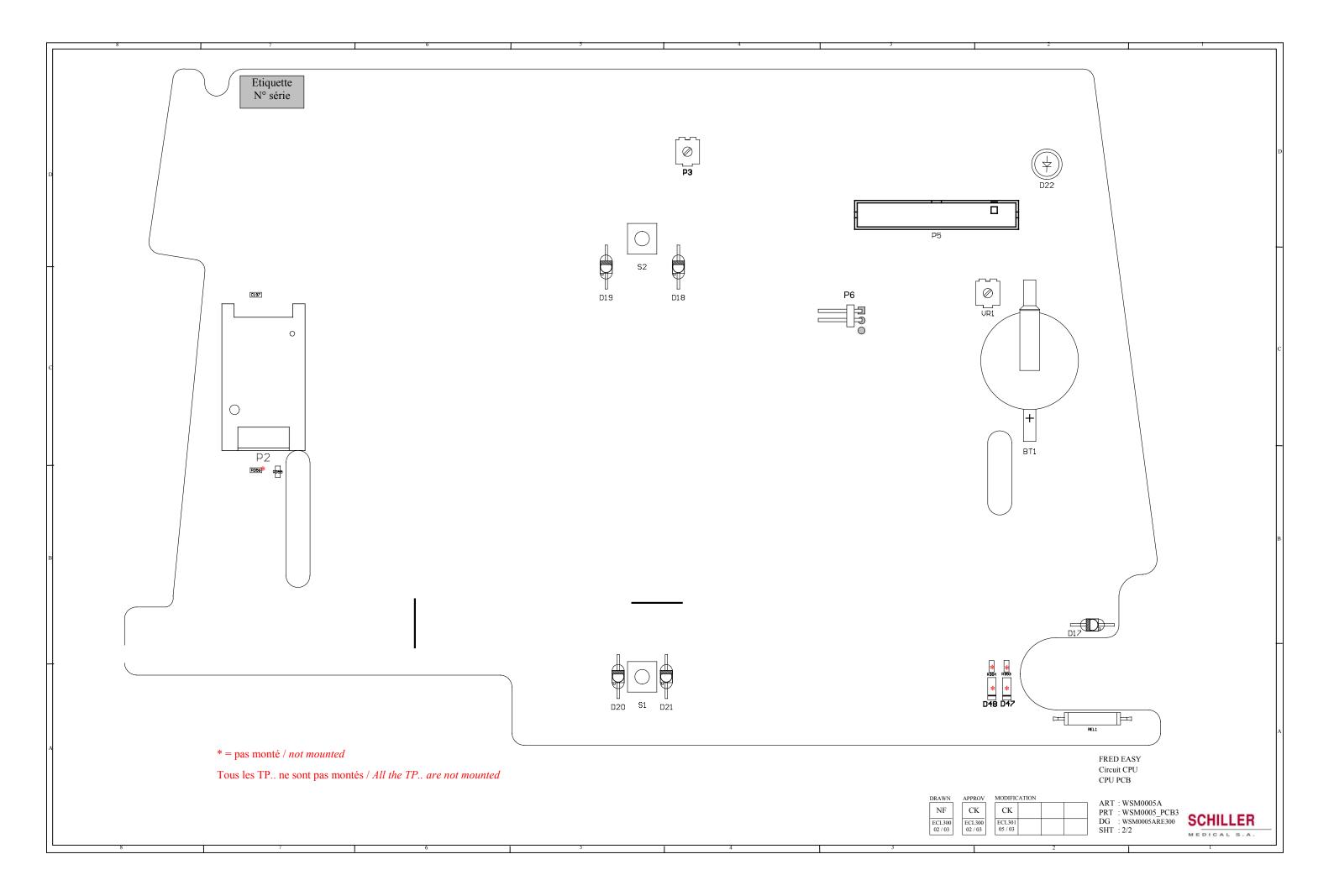

|      | Working on the CPU circuit                                  |              |

|      | Working on the LCD display                                  |              |

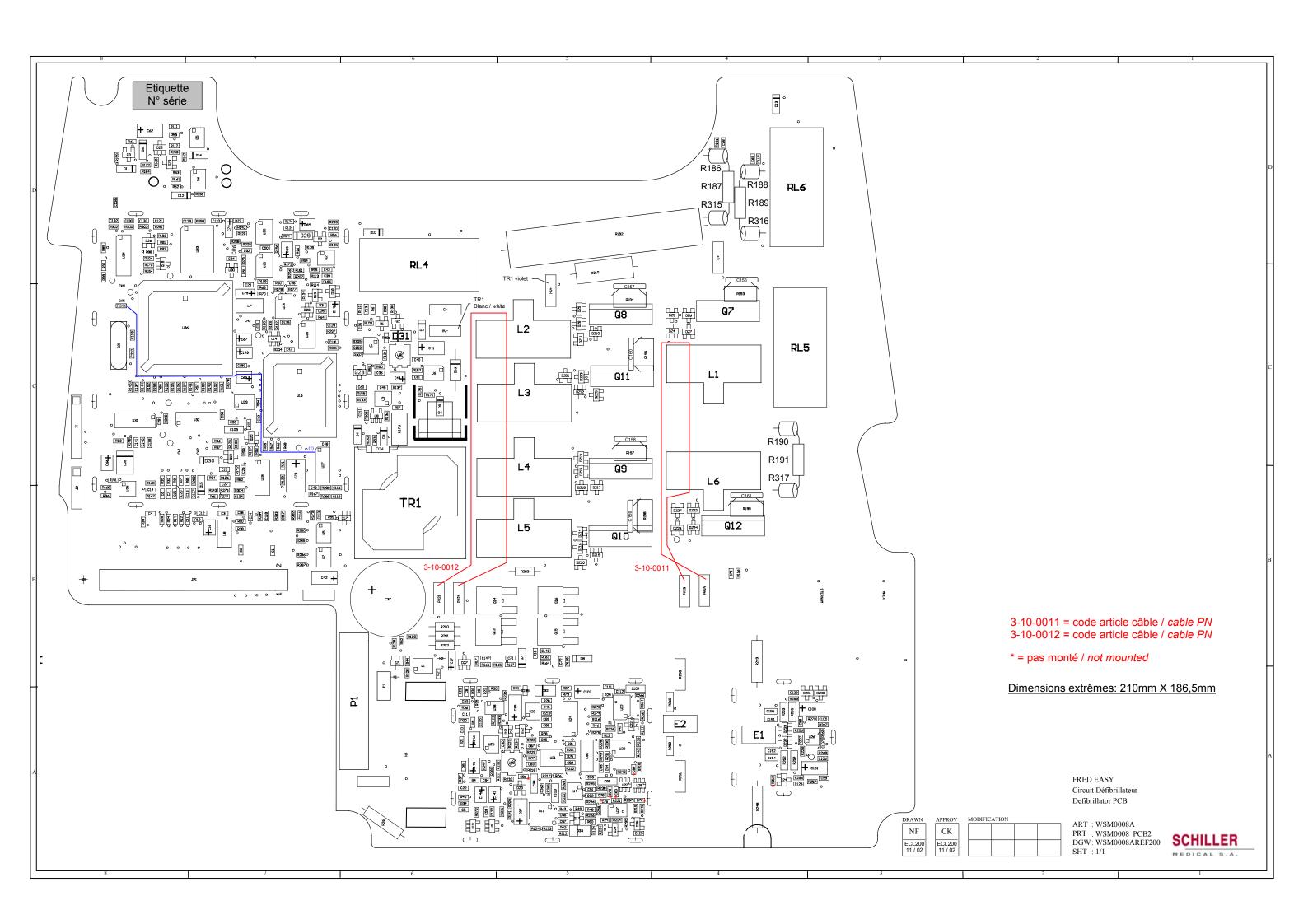

|      | Working on the DEFI circuit                                 |              |

|      | Replacing the high-voltage capacitor                        |              |

|      | Reassembling the device                                     |              |

|      | Replacement of parts                                        |              |

|      | Technical description of boards                             |              |

|      | FRED easy                                                   |              |

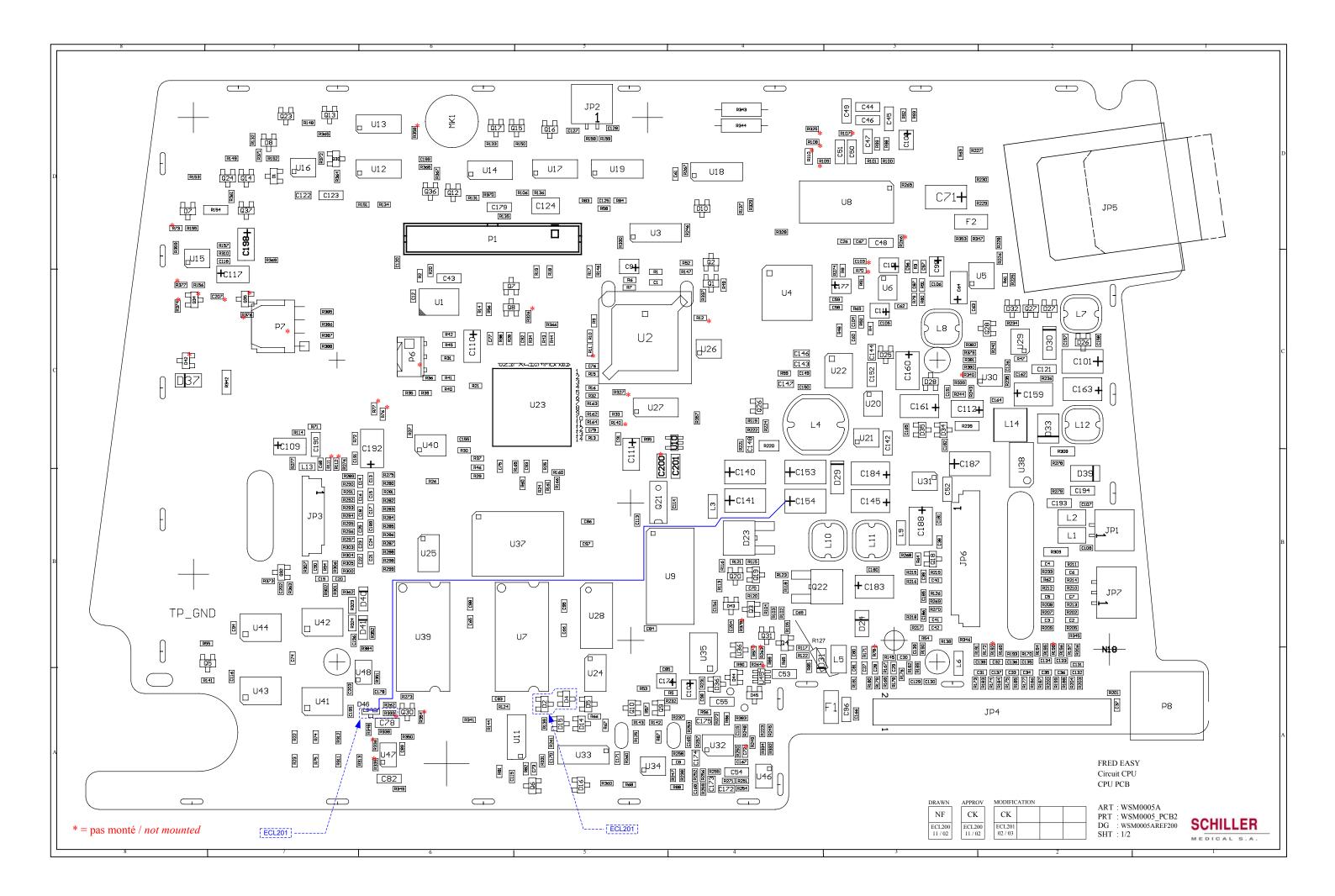

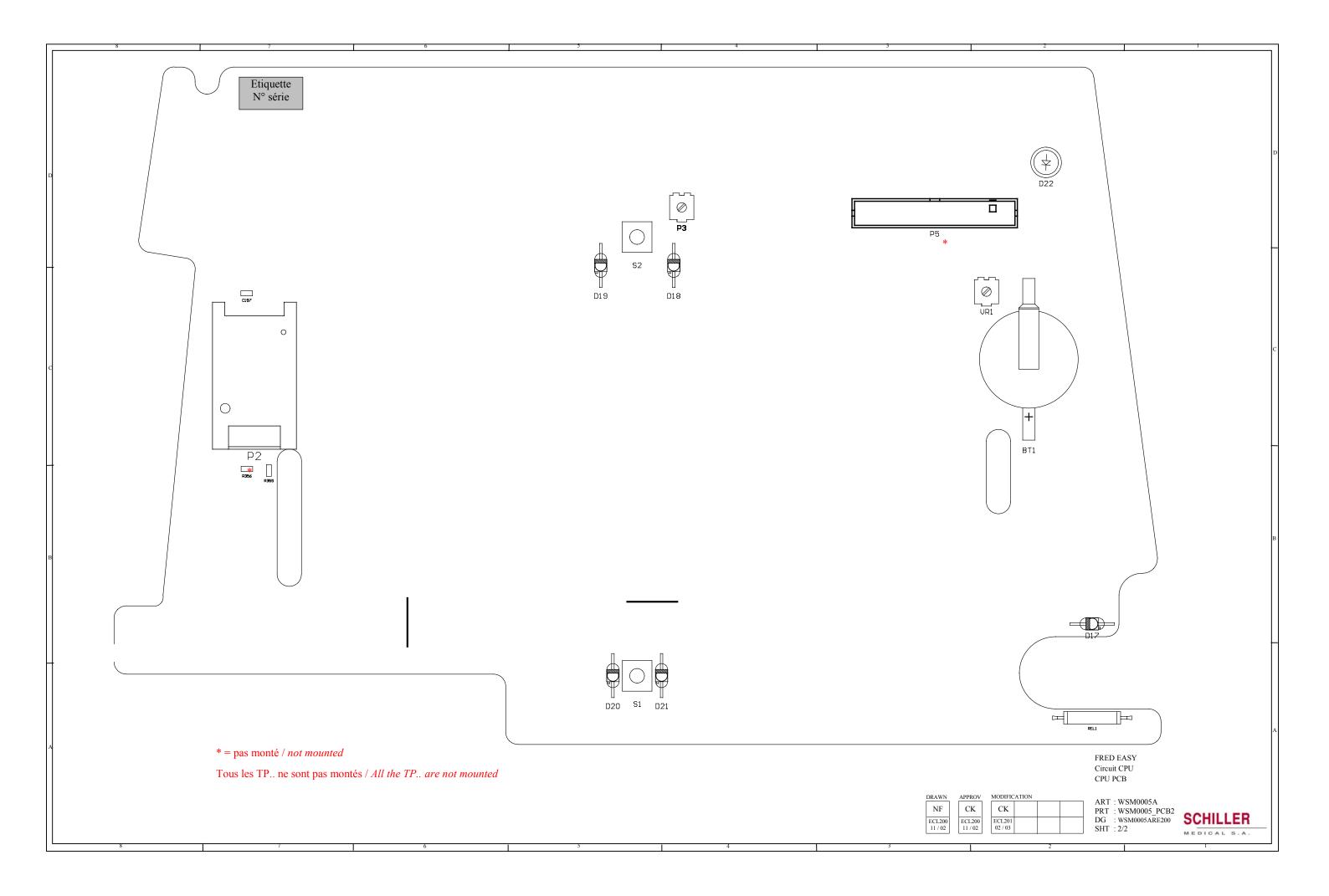

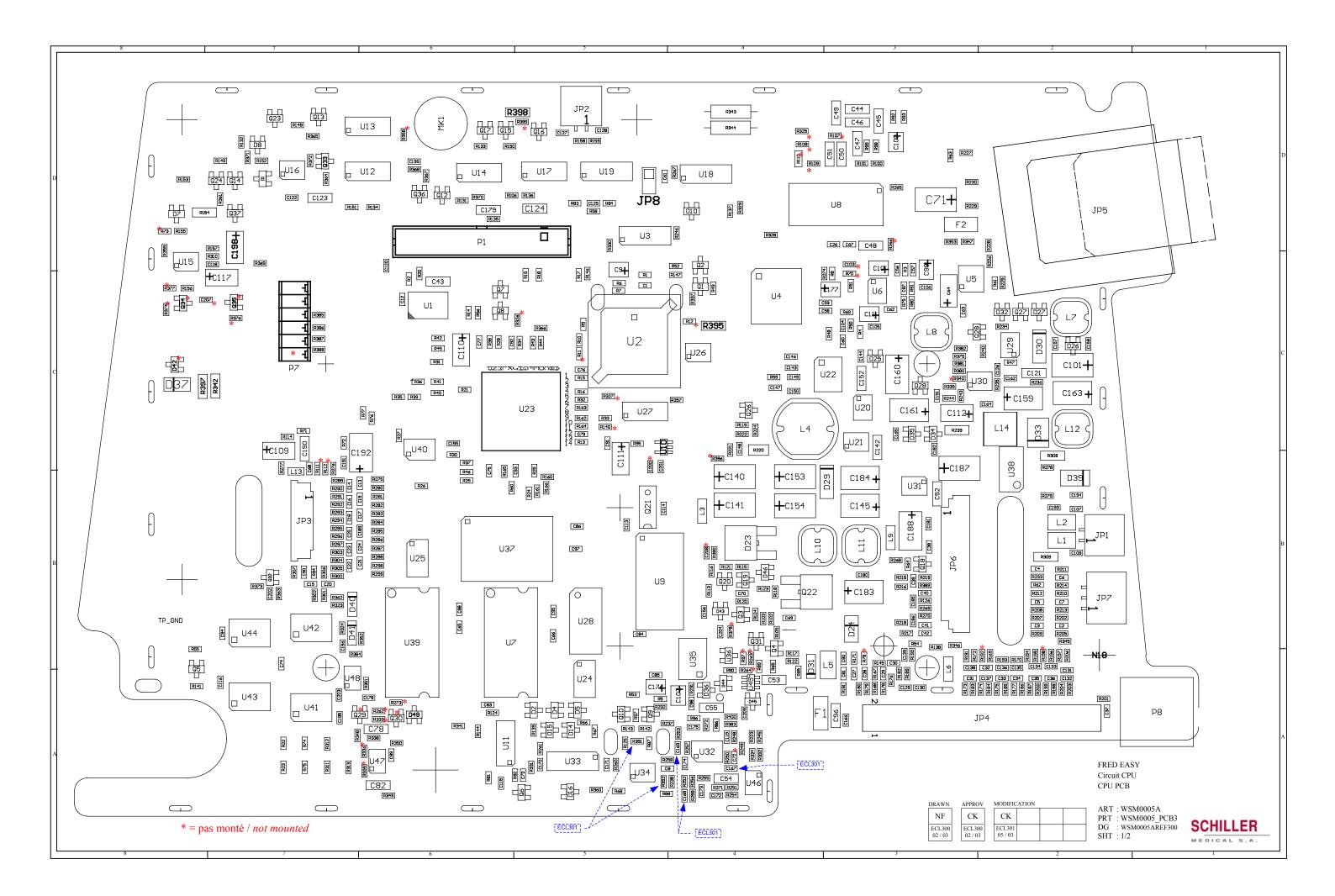

|      | CPU (part no. WSM0005A)                                     |              |

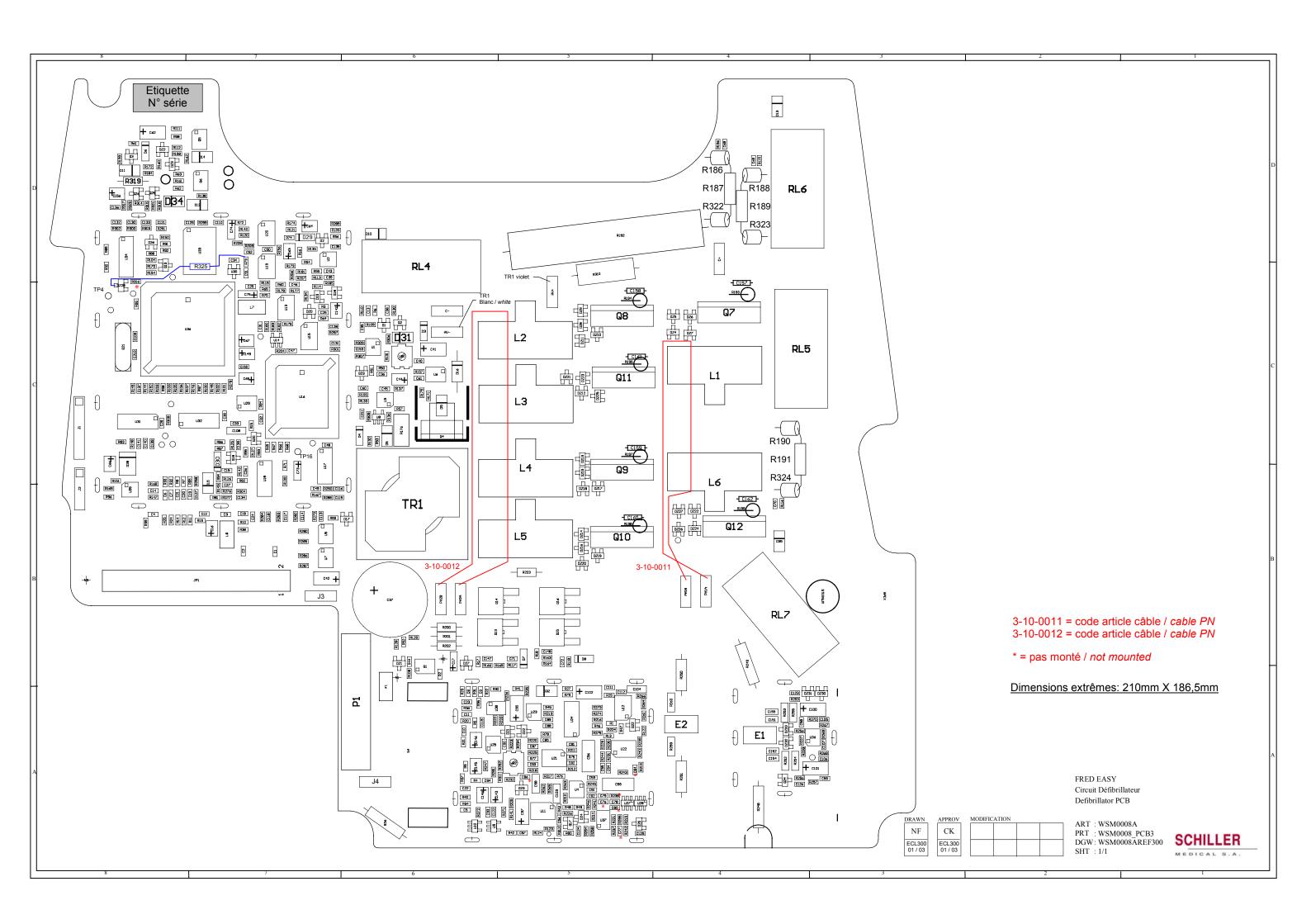

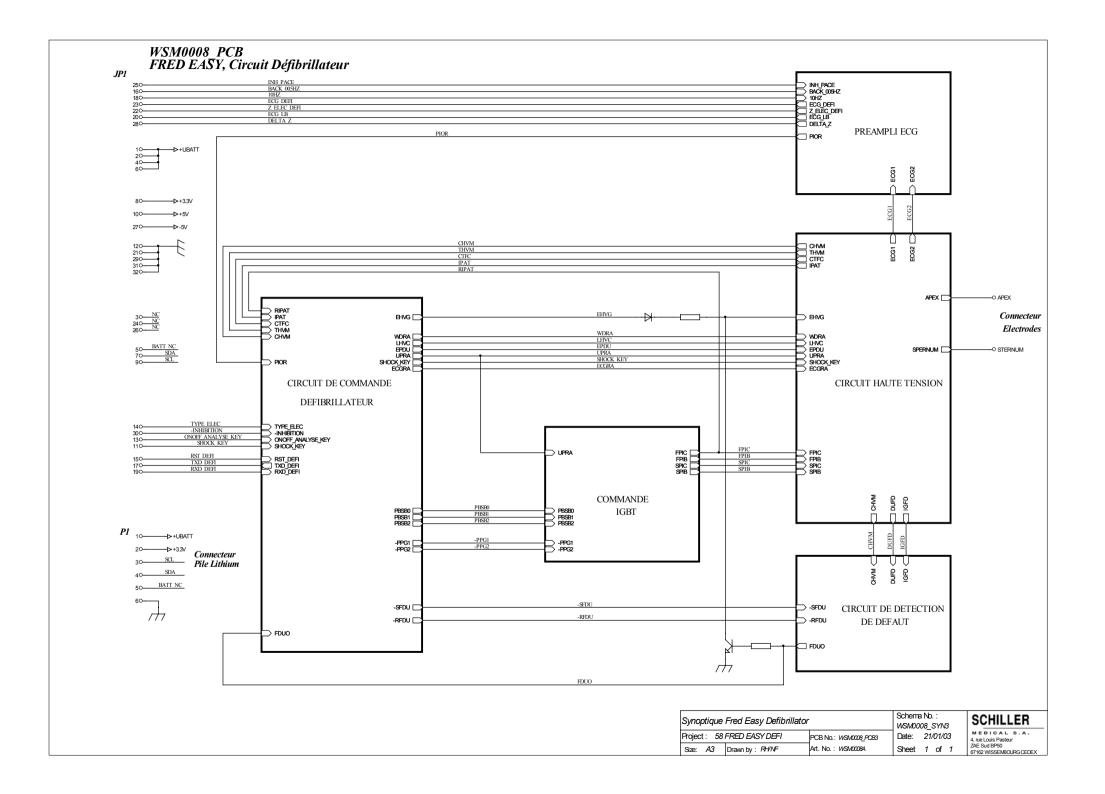

|      | Defibrillator, part no. WSM0008A                            | 5-28         |

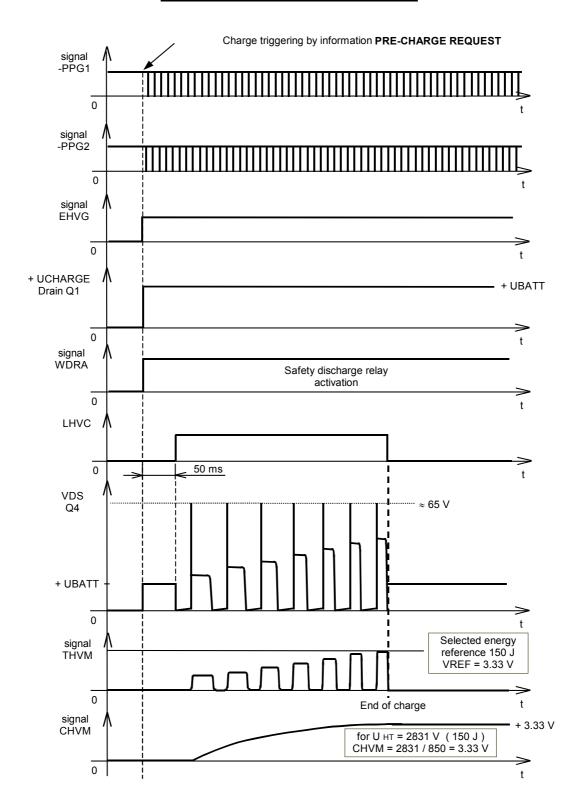

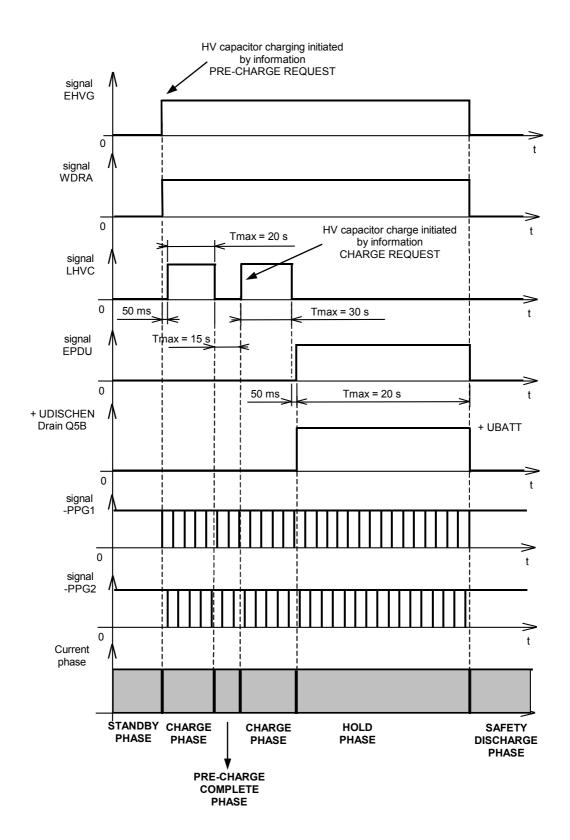

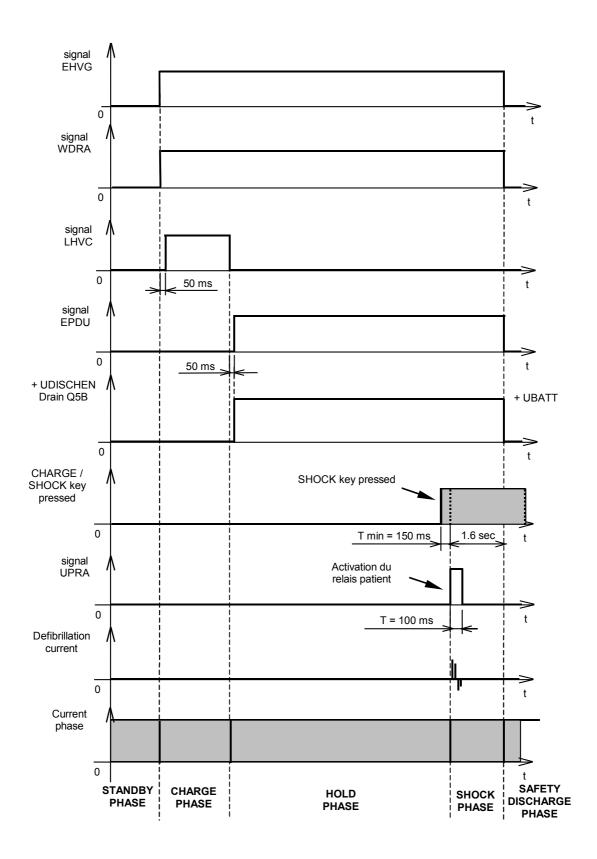

| 5    | 5.3.1 Driving the high-voltage capacitor charge             | 5-33         |

|      | 5.3.2 Chronograms                                           | 5-40<br>5-43 |

| 5    | 5.3.4 ECG preamplifier                                      | 5-43         |

|      | 5.3.4 ECG preamplifier  5.3.5 Defibrillator control circuit | 5-44         |

|      | 5.3.6 High-voltage circuit                                  | 5-48         |

|      | 5.3.8 Fault detection circuit                               | 5-50<br>5-52 |

| 6. E | Device modifications                                        | 6-1          |

|      | Definition                                                  |              |

|      | CPU circuit                                                 |              |

|      | DEFI circuit                                                |              |

|      | Diagrams and layout drawings                                |              |

|      | CPU circuit WSM0005A                                        |              |

|      | Defi circuit WSM0008A                                       |              |

|      |                                                             |              |

# 1. Operation

This section briefly outlines the operating of the device. For more detailed information, please refer to the User's Manual.

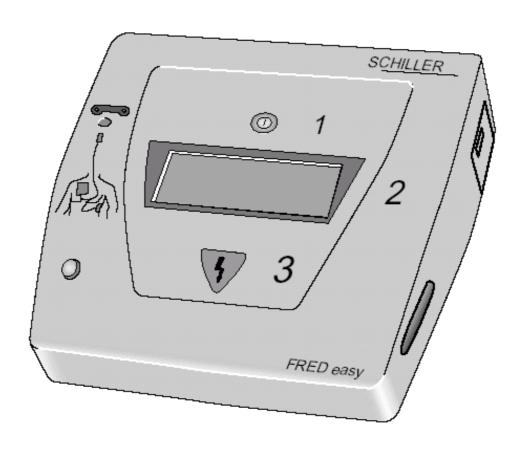

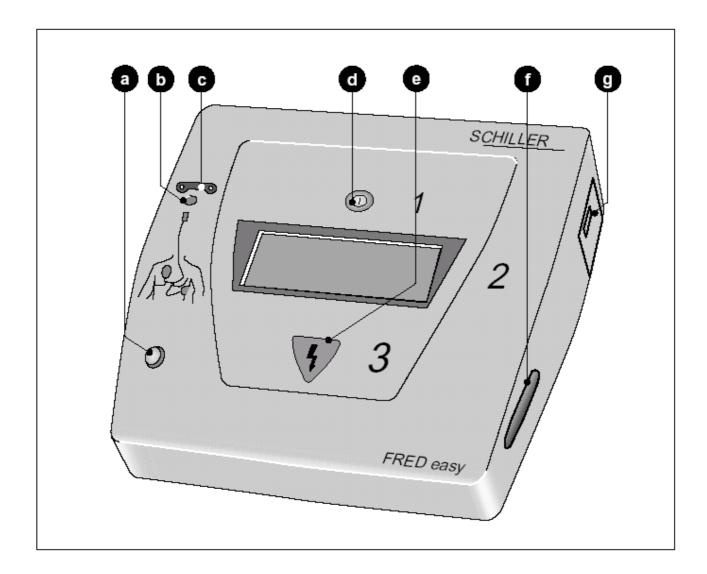

# 1.1 Display and controls

- **a** The green indicator lamp flashes when the device is ready to operate.

- **b** The yellow indicator lamp flashes as long as the electrodes are not in place.

- c Connection of adhesive electrodes

- **d** Green U key to switch the device on and off and start analysing

- e Key for triggering the defibrillation shock

- f Memory card (optional)

- **g** Battery

# 1.2 Explanation of symbols used

Symbols on the device or accessories

| <b>┤</b> ★ | BF type signal input, protected from defibrillation  |  |

|------------|------------------------------------------------------|--|

| 4          | Caution! High voltage!                               |  |

| ×          | Expiry date for the use of defibrillation electrodes |  |

| Â          | Follow the instructions for use                      |  |

|            | Open the electrode packaging                         |  |

|            | Remove the protective film                           |  |

| <b>2</b>   | Single use only. Do not reuse.                       |  |

| <b>X</b>   | Do not fold the packaging                            |  |

|            | Storage temperature range                            |  |

Symbols displayed on the screen

| 5 | Number of shocks given since starting up                    |  |

|---|-------------------------------------------------------------|--|

| • | Battery capacity                                            |  |

|   | Memory card                                                 |  |

| 0 | Memory card not found                                       |  |

| Α | Adult electrode detected                                    |  |

| С | Child electrode detected                                    |  |

|   | Time since the machine was started up (minutes and seconds) |  |

### 1.3 Device operation

FRED easy® is a battery-operated semiautomatic defibrillator that provides biphasic defibrillation pulses.

Defibrillation takes place by means of single-use adhesive electrodes through which the ECG signals required for the analysis are also collected. Adhesive electrodes are available for children and adults. The device recognises the type of electrode applied and selects the defibrillation energy values accordingly.

The user is provided with written and audio instructions (display and loudspeaker) relating to the use of the device.

The power is supplied by plug-in disposable lithium batteries. Their capacity is sufficient for

- 200 shocks at the maximum power rating or

- use of the monitor for seven hours (cyclical, 30 minutes on, 30 minutes off) or

- 5 years standing by.

As soon as a battery is put in place in the **FRED easy®** device, it runs a self test to check the status of the device and battery. If the device does not find any fault, the green indicator begins to flash to show that it is ready to operate and the display disappears. Likewise, the device runs a self test each time it is switched on.

If, during the test, the device finds an error:

- it issues an audio alarm,

- the green indicator does not flash

The alarm signal rings till the battery is completely discharged. Key () is used to repeat the self test and the error message is displayed.

Also, the device runs a self test after every seven days. The test is announced by a beep. If, during the test, the device finds an error:

- it issues an audio alarm,

- the green indicator does not flash

If you press key (1) the corresponding error message is displayed.

In that case, you must replace the battery and repeat the test. Depending on the test result, the error message will disappear or another message will be displayed.

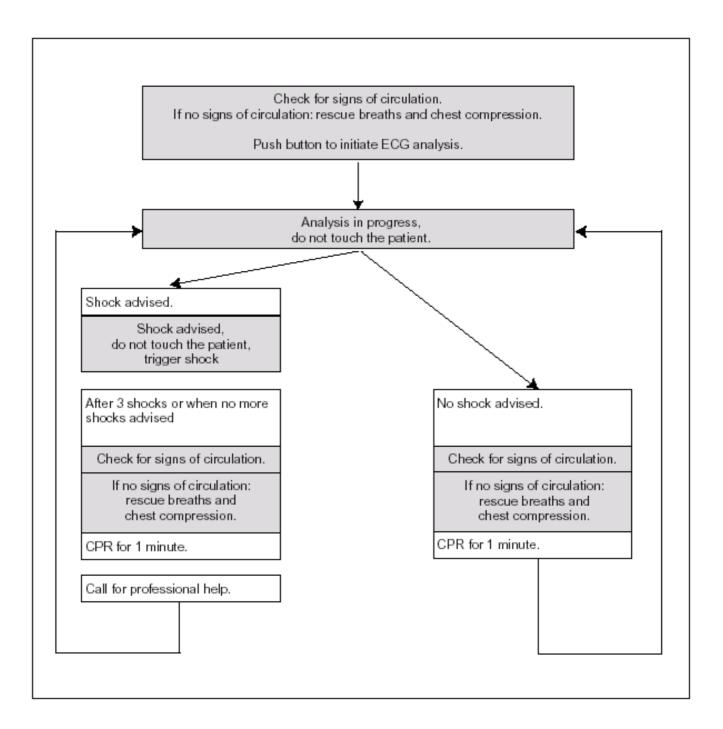

# 1.4 Defibrillation procedure

All the stages are explained orally to the user at the same time as they are displayed on the screen. Once key (1) is pressed, the introductory text tells the user what is to be done if the patient has the following symptoms:

- the patient has ceased to breathe,

- there is no sign of circulation.

The introductory text is repeated till the **FRED easy®** device recognises the application of the adhesive electrodes. Depending on the configuration, the introductory text may be deleted and the device directly requests the application of the adhesive electrodes.

After that, the **FRED easy**® device asks the user to start an ECG analysis and to no longer touch the patient. The analysis lasts approximately 10 s. Depending on the configuration, the device starts the ECG analysis automatically.

#### Note

- With the signals from the AHA (American Heart Association) database, the detection accuracy of **FRED easy**® was found to be 98.43 % (sensitivity), with a specificity rate of 99.80 %.

- The device may be configured so that it automatically starts the ECG analysis.

If the analysis program recognises a heart rate that calls for defibrillation, it automatically charges the energy required for defibrillation and asks the user to deliver the shock after the energy is charged.

The following are considered to warrant defibrillation:

- ventricular fibrillation or

- ventricular tachycardia with a heart rate of over 180 bpm.

If the device finds a heart rate that calls for defibrillation, defibrillation is only authorised if the patient is found to have no pulse or if there are no signs of circulation.

If the defibrillation shock has no effect, the device automatically charges the energy required for a second or even a third shock.

| Note         |                     |                     |                                               |

|--------------|---------------------|---------------------|-----------------------------------------------|

| The energ    | y values are set b  | by default as follo | ows (the technical assistance of SCHILLER can |

| configure of | other default value | es if needed).      |                                               |

| _            | Shock               | Adult               | Child                                         |

|              | 1                   | 90 J                | 15 J                                          |

30 J

50 J

If the third shock is also ineffective, the **FRED easy**® device asks to user to alternately administer artificial respiration and heart massage. After a minute, an ECG analysis will be requested once again. Depending on the configuration, the new analysis may be automatic.

After a successful defibrillation shock, the **FRED easy®** device asks the user to check the patient's breathing and blood circulation. If there is no sign of circulation, the device asks the user to alternately administer artificial respiration and heart massage. If there is any sign of circulation, the patient must be laid on his or her side.

If the analysis program does not recognise a heart rate calling for defibrillation,

- FRED easy® informs the user that defibrillation is not necessary and

130 J

150 J

- asks the user to look for breathing and signs of circulation.

If there is no sign of circulation, the **FRED easy®** device asks the user to alternately administer artificial respiration and heart massage. If there are any signs of circulation, the user is asked to lay the patient on his or her side.

After a minute, the **FRED easy**® device repeats the request for an ECG analysis. Depending on the configuration, the new analysis may be automatic.

The following values can be configured by the technical assistance department of SCHILLER:

- upon starting up: introductory text or immediate request to apply the adhesive electrodes,

- voice volume,

2

- energy levels of shocks 1, 2 and 3, with adult and child separate

- starting of the ECG analysis via the keypad or automatically.

# Procedure chart

# 1.5 Recording (optional)

For information, the memory board can save the following:

- half an hour of ECG

- half an hour of speech,

- 500 events relating to the procedure (see overview opposite).

| Plugging in a memory card activates the memory function and the display includes the icon $\overline{\square}$ . |

|------------------------------------------------------------------------------------------------------------------|

| The memory card is analysed by means of a PC, with the SAED Reader software.                                     |

| Icon I flashes when the memory card is full.                                                                     |

Important! The device must be switched off when you insert the card. Otherwise, the device will not recognise the card and will display the following symbol:

If no symbol is displayed even after the card has been put in place, you must make sure that the card is indeed a card designed for such devices by SCHILLER.

# 1.6 Technical specifications

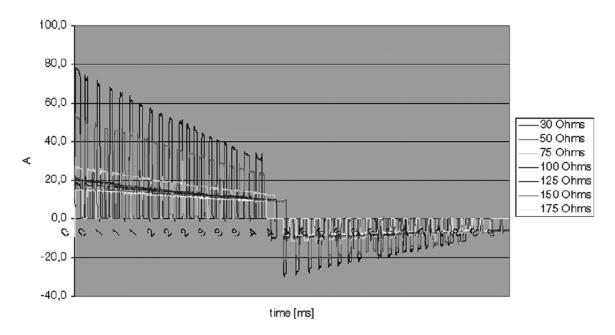

- · Form of the defibrillation pulse

- Modulated defibrillation pulse with two pulse phases and physiologically optimised phase duration of 4 ms.

- Constant value of the average current delivered and the energy discharged depending on patient impedance, using pulse modulations in the pause position in the two phases.

- Modulation of the second phase (negative phase) so that the residual charges of the first phases are degraded in the heart.

- Standard energy settings:

- Adult (discharge in 50 .): 90 -130 -150 J

- Child (automatic switch when child electrodes are connected): 15 -30 -50 J

- The energy levels can be configured by the technical assistance department of Schiller if the standard values need to be changed:

- Tolerance at 50  $\Omega$ :  $\pm$  3 J or  $\pm$  15 % (whichever is greater).

- Automatic charge control after a shock is recommended following an analysis

- Patient resistance 30 175 .

- Charge duration, from the time a shock is recommended up to the time when the device is ready:

10 s

- Cycle time between two shocks:

< 20 s</li>

- Indication that the devices is ready to deliver a shock: key younger

- The shock is delivered with key

- Internal safety discharge if:

- the heart rate does not call for defibrillation

- after 20 seconds of the device indicating its readiness for a shock, no shock is delivered

- there is an electrode fault

- the battery voltage is insufficient

- the device is faulty

- the device is switched off

- The shock is delivered with single-use adhesive electrodes applied in the anterior / anterior-lateral positions

- BF type defibrillation electrode connector.

- Defibrillation electrodes:

- Adult electrodes: Active area 78 cm²

Child electrodes: Active area 28 cm²

- Electrode cable length: 2 m

- VT / VF recognition:

- Shock recommendation: for VF and VT (VT > 180 bpm)

- Sensitivity: 98.43 %

Specificity: 99.8 %. These values have been found with the AHA database, which contains cases of VF and VT with and without artefacts.

- Conditions required for ECG analysis:

Minimum amplitude for the signals used > 0.15 mV, signals of < 0.15 mV are considered to show asystole.

- Definition:

Sensitivity: Correct detection of heart rates for which defibrillation shocks **are** recommended Specificity: Correct detection of heart rates for which defibrillation shocks **are not** recommended

- Display:

- LCD, 100 x 37 mm, high definition, with EL backlighting, display of text and icons.

- Recording of the use of the device (optional)

- ECG recording (half an hour)

- Voice recording (half an hour)

- Event recording (500 events)

- Lithium battery capacity

- 200 shocks at the maximum power rating or

- Use of the monitor for seven hours (cyclical, 30 minutes on, 30 minutes off)

- Five years standing by.

- Environment conditions:

- Transport / storage:

Temperature - 30 to + 50 °C

Relative humidity of air 0 to 95 %, non condensing

Atmospheric pressure 500 - 1060 hPa

- Use:

Temperature - 30 to + 50 °C

Relative humidity of air 0 to 95 %, non condensing

Atmospheric pressure 700 - 1060 hPa

- Electromagnetic compatibility:

- The **FRED easy**® device only uses radio frequency range energy for its internal functions. It is treated against interference in accordance with standard CISPR 11 class B

- The **FRED easy**® device can be subjected to the following interference without any adverse effect on its functioning:

- electrostatic discharges of up to 8 kV.

- energy in the radio frequency range up to 20 V/m (80 2500 MHz, 5 Hz modulated).

- magnetic fields of 100 A/m, 50 Hz

- Dimensions and weight:

- Width : 220 mm - Depth : 230 mm - Height : 70 mm

- Approximate weight : 1.5 kg (with battery)

# 2. Testing and maintenance

This section describes the testing and maintenance procedures recommended for FRED easy.

# 2.1 Functional testing

The device runs an automatic functional test. In order to ensure proper performance, tests are performed when the device starts in the nominal mode (SAD mode), once a week and each time a battery is inserted. The Test mode defines specific device behaviour and is used to test its vital functions. The functioning of the Test mode is not redundant with the self test phase. The aim of the self test is to check the vital functions of the device when it is switched on. The aim of the Test mode is to regularly check the vital parts of the device in order to ensure that it will continue to perform even when it is used occasionally.

The device is also in the Test mode when a battery is inserted. In that case, specific tests are defined.

#### Specific case of self tests:

Self tests are performed automatically when the device is switched on and require no action by the operator. No message describing the test under way is displayed when the device runs its self tests. A message is displayed to merely show that the device is about to start – "STARTING…".

The software version of the device is also displayed during the self test.

The self test consists in checking the following functions:

- ADC converter test it is used to validate the functioning of the analogue to digital converter used to acquire battery parameters (voltage and temperature) and patient parameters (ECG 250Hz, MVTS, impedance variation, patient impedance)

- Defibrillator test, level 1 used to validate the status of the defibrillator hardware and particularly to

ensure that communication with the defibrillator is operational and that the defibrillation hardware module

has not found any error.

- EEPROM configuration test it is used to make sure that access to the EEPROM containing device configuration information is valid and that the information is consistent

- RTC test used to validate the operating of the real time clock of the device

- Battery test used to validate the battery level (the test shows an error if the remaining battery charge is 0%)

- LCD test used to validate the display

- OKI test used to validate the speech prompt system

- Encoder test used to validate the operating of the sound environment acquisition system

If any of the tested peripherals shows an error, the device cannot be used. In that case, the device status display (flashing LED) is changed to indicate that the device may not be used – the LED goes off – and a message indicates the test that has failed. When the LED goes off, a buzzer is triggered to indicate a device fault.

If the tests succeed, the device executes the SAD operating mode.

#### **Specific case of periodic tests:**

Because the device is used in emergency situations, it must be ready to operate when it is needed. As a result, self tests are insufficient. That is why periodic testing is performed to maximise the chances of detecting any error in the device, including when it is not used.

Periodic testing includes the following operations:

- Self tests

- Level 2 hardware test of the defibrillator module test of a battery test command by the defibrillator module. This test is used to check that the power source of the device (lithium cell or battery) makes it possible to charge the device.

- ECG acquisition circuit test checking the functioning of the ECG signal acquisition chain, which acts as the basis for analysing the patient's heart signal. This test is used to make sure that the data on which the diagnostic is based are consistent.

The tests are performed automatically from time to time. Every week at 12.00 hours, the tests are performed if the device is off. The clock wakes the device for the requisite operations. The alarm date is configurable by means of the configuration PC.

Periodic tests are logged in order to be able to determine the nature of any failure and the time when the failure occurred. The last thirty results of periodic testing are logged in the memory. The memory can be read simply by means of a PC, in the configuration and transfer mode. That makes it possible to identify the origin of the problem found.

The logged data include the following:

- test date

- test time

- test result

- origin of the problem found, if the result shows an error

The detection of a problem during a periodic test makes the device impossible to use. The Status display is changed in order to indicate that a problem has been found. Nothing is displayed during the periodic tests in order to maximise the use of machine power. That is why the Status display is the only means of indication.

When the device is switched on again, an error message indicates the problem found during periodic testing. Each time the device is switched on, the error message is displayed. The error disappears when the problem is corrected and when new tests succeed after battery insertion.

If the tests are successful, the device is switched off.

#### Specific case of battery insertion tests:

Given that periodic tests cannot be performed when the device no longer has a battery, the device must be tested as soon as a new battery is inserted, in order to indicate any fault as soon as possible. Tests are triggered as soon as a battery is inserted in the device.

In that case, the test and the operations performed are:

- Self tests if no error is found during previous periodic tests

- Self tests, level-2 hardware test of the defibrillator module and ECG acquisition circuit tests, if an error has been found during the previous periodic tests.

If any of the tested peripherals shows an error, the device cannot be used. In that case, the device status display (flashing LED) is changed to indicate that the device may not be used – the LED goes off – and a message indicates the test that has failed.

If the battery insertion test is successful and if the last logged periodic test has failed, the battery insertion test is logged. The logged data include:

- test date

- test time

- test result OK

- reset information, to indicate that a problem had been found during periodic tests and has been corrected.

If the tests are completed successfully, the device goes off automatically at the end of the operation. Otherwise, the device stays on to indicate the failed test.

# 2.2 Systematic verification before use

Before each use of the device, the device, cables, connectors and electrodes must undergo a visual inspection.

If you find any faults or malfunctioning that could impact the safety of the patient or the user, do not use the device before it is repaired.

Systematic verification before each use

- Verification of the device housing

- No mechanical damage

- No penetration of liquid in the device

- Check the condition of the control buttons and the connectors.

# 2.3 Cleaning and disinfecting

Caution:

Switch the device off before cleaning it. Remove the cell before you start cleaning the device in order to eliminate the risk of the device starting up accidentally. Also disconnect the defibrillation electrodes of the device before cleaning.

No liquid shall be allowed to enter into the device. However, if that does happen, the device may not be used before it is verified by the after-sales service department.

The device or electrodes may never be cleaned with substances such as ether, acetone, esters, aromatic chemicals etc.

Never use phenol-based cleaners or cleaners containing peroxide derivatives to disinfect the surfaces of the housing of the device.

- Dispose of all single-use electrodes immediately after use in order to eliminate the risk of accidental reuse (disposal with hospital waste).

- Before cleaning the electrode cables of sensors, disconnect them from the device. For cleaning

and disinfecting, wipe the cables with a gauze cloth moistened with cleaner or disinfectant.

Never immerse the connectors in liquid. The cleaning solution used may be any cleaning or

disinfecting solution that is commonly used in hospitals.

- Proceed likewise with the device housing, with a cloth moistened with cleaner or disinfectant. No liquid may be allowed to penetrate into the device during the operation.

# 3. Troubleshooting

This section addresses the troubleshooting procedures for **FRED** easy®. If you have trouble locating or correcting the problem, contact the after-sales service department of Schiller.

### Precautions during troubleshooting

While testing the FRED EASY defibrillator, the patient may only be simulated with fixed high-voltage and high-power resistors that are well insulated from the ground or earth. Poorly insulated devices or devices with loose contacts or devices containing components such as spark arresters or electronic flash lamps may never be used as they could irremediably destroy the device.

The user's manual contains a troubleshooting table intended for the user.

| ERROR                                                                                    | FINDING                             | POSSIBLE CAUSES                                                                                                                            | CORRECTIVE ACTION                                                               |

|------------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| The device is not switched on when the battery is inserted.                              |                                     | Cell fault     Incorrect insertion     Problem with contacts     Problem with fuses                                                        | Replace the cell     Repeat the insertion     Check contacts     Check fuses    |

| When the cell is inserted, to but the OK indicator does                                  |                                     | Fuse F1 on CPU board faulty                                                                                                                | 1. Replace fuse                                                                 |

| No display of message:<br>FRED IS TESTING                                                |                                     | 1. Check the button cell on the CPU (out of order or down) 2. Check if F1 is faulty on DEFI board 3. CPU board faulty 4. DEFI board faulty | 1. Replace the button cell 2. Replace fuse 3. Replace CPU 4. Replace DEFI board |

| When the cell is inserted, no self test but the OK indicator flashes.                    |                                     | 1. CPU board faulty                                                                                                                        | 1. Replace CPU                                                                  |

| The self test succeeds, but the OK indicator does not flash. The screen stays on for 5 s |                                     | 1. CPU board faulty                                                                                                                        | 1. Replace CPU                                                                  |

| The On/Off key does not respond.                                                         | No display and/or no voice messages | 1. CPU board faulty                                                                                                                        | 1. Replace CPU                                                                  |

| Message:<br>DEFIBRILLATOR<br>CPU ERROR                                                   |                                     | 1. DEFI board                                                                                                                              | 1. Replace DEFI board                                                           |

| Message:<br>DEFIBRILLATOR<br>INTEGRITY ERROR<br>PROGRAM                        |  | 1. DEFI board                 | 1. Replace DEFI board                    |

|--------------------------------------------------------------------------------|--|-------------------------------|------------------------------------------|

| Message:<br>DEFIBRILLATOR<br>DETECTOR ERROR                                    |  | 1. DEFI board                 | 1. Replace DEFI board                    |

| Message:<br>DEFIBRILLATOR ERRO<br>VOLTAGE REFERENCE                            |  | 1. DEFI board                 | 1. Replace DEFI board                    |

| Message:<br>DEFIBRILLATOR<br>CONVERTER ERROR<br>ADC                            |  | 1. DEFI board                 | 1. Replace DEFI board                    |

| Message:<br>DEFIBRILLATOR<br>CHARGE TRANSISTOR<br>ERROR                        |  | 1. DEFI board                 | 1. Replace DEFI board                    |

| Message:<br>DEFIBRILLATOR<br>SAFETY DISCHARGE<br>ERROR                         |  | 1. DEFI board                 | 1. Replace DEFI board                    |

| Message:<br>DEFIBRILLATOR<br>EPROM ERROR                                       |  | 1. CPU board                  | 1. Replace CPU board                     |

| Message:<br>DEFIBRILLATOR<br>SHOCK BUTTON ERROR                                |  | 1. CPU board<br>2. DEFI board | Replace CPU board     Replace DEFI board |

| Message: DEFIBRILLATOR COMMUNICATION ERROR                                     |  | 1. CPU board<br>2. DEFI board | Replace CPU board     Replace DEFI board |

| Message:<br>SYSTEM ERROR                                                       |  | 1. CPU board                  | 1. Replace CPU board                     |

| Fault detected during the self test  Monitor on, but the OK LED does not flash |  | 1. CPU board                  | 1. Replace CPU board                     |

|                                                      |               | <u>"</u>                               |                                             |

|------------------------------------------------------|---------------|----------------------------------------|---------------------------------------------|

| Cell symbol flashing, but no remaining %             |               | 1. Cell contact fault                  | 1.1 Check cell contact     1.2 Replace cell |

| Electrodes not connected electrode connection off    | and LED under | DEFI board faulty     CPU board faulty | Replace DEFI board     Replace CPU board    |

| Electrodes connected to si impedance, but the LED do |               | DEFI board faulty     CPU board faulty | Replace DEFI board     Replace CPU board    |

| No cell voice message                                |               | Speaker fault     CPU board fault      | Replace speaker     Replace CPU board       |

| Device off, OK LED off and no buzzer                 | Audio alarm   | Buzzer fault     CPU board fault       | Replace buzzer     Replace CPU board        |

| Green Analysis key or orange Shock key not on        |               | 1. CPU board fault                     | 1. Replace CPU board                        |

| Abnormal internal discharge                          |               | 1. DEFI board faulty                   | 1. Replace DEFI board                       |

| No shock delivered                                   |               | DEFI board faulty     CPU board fault  | Replace DEFI board     Replace CPU board    |

| No record on memory card                             |               | Memory card     CPU board fault        | Replace memory board     Replace CPU board  |

| Loss of date and time                                |               | Button cell     CPU board fault        | Replace button cell     Replace CPU board   |

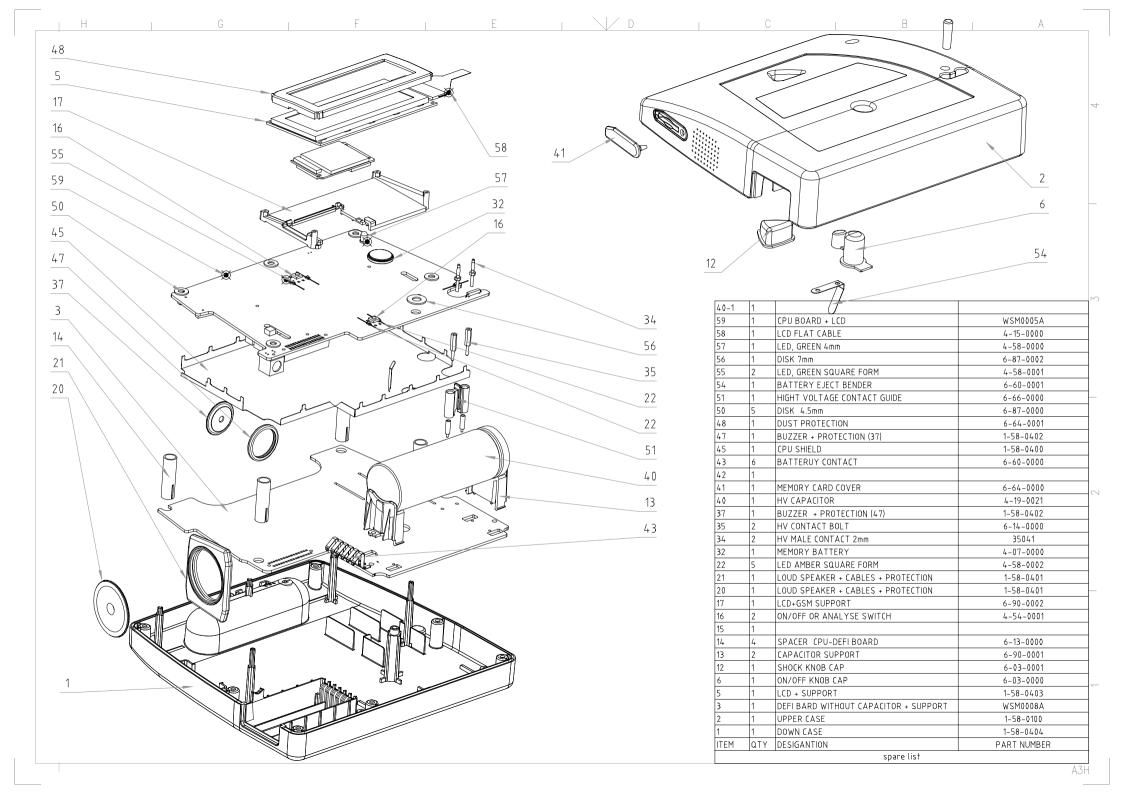

# 4. Replacement of parts

This section addresses the issue of how to dismantle **FRED** easy in order to replace faulty parts. The warnings below apply to all work inside the device.

| Warning: | FRED easy is a defibrillator with a high-voltage capacitor that can be charged to a fatal voltage. The device may only be |

|----------|---------------------------------------------------------------------------------------------------------------------------|

|          | dismantled by specially authorised and trained personnel.                                                                 |

Caution: Before dismantling the device, remove the battery or the cell from its slot.

Caution:

The device contains circuits sensitive to electrostatic discharge. All work on the FRED® easy device shall be performed in accordance with ESD rules. The repairs shall be performed on an antistatic mat connected to the earth and the operator shall wear an antistatic strap also connected to the mat. In the event of any work on the high-voltage part of the defibrillator, remove the antistatic strap.

Caution:

During the replacement of one of the boards, it should absolutely be seen whether the versions are compatible by consulting the table available at Schiller Medical. Only the versions are compatible which comprise a HARDWARE

number in the table of the versions.

On your device, the HARDWARE version number perhaps consulted only with the module of remote loading. For each replacement of chart, it is necessary to charge the good

Caution: A general device test shall be performed each time the device is opened.

number of HARDWARE version given speaks table.

# 4.1 Device disassembly procedure

Follow the points below while disassembling the device:

- 1. Remove the Lithium cell from its slot.

- 2. Disconnect the electrode cables.

- 3. Turn the device over (LCD screen down) and unscrew the nine assembly screws of the two (upper and lower) halves of the housing.

- 4. After removing the nine screws turn the device over (LCD screen facing you).

- 5. The upper half can now be removed by pulling it up gently. The electrode connections to the left and the speaker to the right of the device may offer some resistance. In order not to pull off the speaker wires, hold it in the lower part while removing the upper part.

Caution:

Take care not to lose the caps of the control buttons placed in the upper part.

# 4.2 Working on the CPU circuit

Follow the instructions below to remove the CPU:

- Remove the six rubber washers.

- 2. Disconnect the CPU from the connector to the rear of the device near the battery slot.

- 3. Take off the buzzer and the speaker of the lower housing and carefully pull the connectors.

Caution: The circuit includes components that are sensitive to electrostatic discharge. The work described above shall be performed in accordance with ESD rules.

#### 4.3 Working on the LCD display

After removing the CPU PCB, the LCD display can be removed by following the instructions below:

- 1. Carefully remove the connector of the backlighting circuit connected to the CPU.

- 2. Remove the connector of the flat jumper.

- 3. Unscrew the four screen fastening screws.

The liquid crystal display is a version with backlighting. The two functions cannot be dissociated. If the display is to be replaced, make sure the new screen is clean. Never clean the surface of an LCD screen with cloth or paper that could be very slightly abrasive and scratch the screen. Any dust should be removed by blowing compressed air.

# 4.4 Working on the DEFI circuit

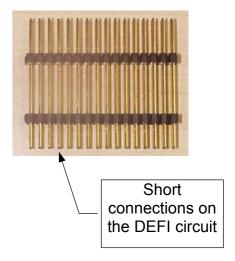

To remove the DEFI circuit, remove the spacers and pull out the circuit, which is just placed inside the housing.

Caution: The circuit includes components that are sensitive to electrostatic discharge. After the PCB is disconnected from the device, comply with ESD rules.

#### 4.5 Replacing the high-voltage capacitor

Warning: This operation relates to the high-voltage capacitor, which can carry fatal charges. Before starting to work, take care to discharge the high-voltage capacitor completely. The terminals of the high-voltage capacitor must never be touched directly. The high-voltage capacitor may never be replaced by people other than specially authorised and trained personnel.

The replacement of the high-voltage capacitor is an extremely rare operation, as the life of the capacitor is very long. However, if needed, the high-voltage capacitor may be replaced in accordance with the following instructions:

- 1. Disconnect the two Faston lugs

- 2. Take the capacitor off its support

After removing the (fully discharged) high-voltage capacitor from the lower part, short the three terminals of the capacitor with conducting wire.

While replacing the high-voltage capacitor, glue it to the support, twist the wires and wire them in accordance with the polarity requirements. The wires are to be routed as required. Make sure that nothing has been forgotten before the device is started up again.

Caution:

This operation relates to an essential component of the high-voltage part. It may only be performed by specially authorised personnel who have been trained in repairing FRED® easy devices.

The delivered energy must undergo testing.

# 4.6 Reassembling the device

To put back the device, reverse the procedures.

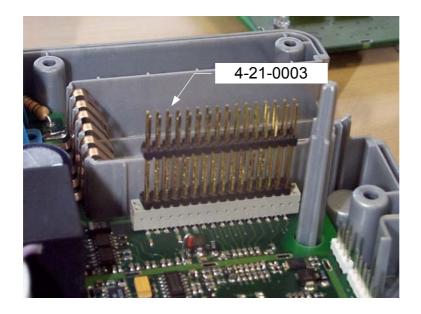

#### Instructions for assembling the connector between boards:

# 4.7 Replacement of parts

Warning:

Parts may only be replaced by personnel who have been specially trained and authorised by Schiller Medical.

Besides, the replacement parts shall be original Schiller Medical parts.

Note:

To order a new part from Schiller Medical, provide the part number and the serial number of the device located under the device. After that, specify the item code of the part, the part number, the description provided in the list of parts and the ECL of the replaced part.

# 5. Technical description of boards

# 5.1 FRED easy

#### **General description of FRED easy:**

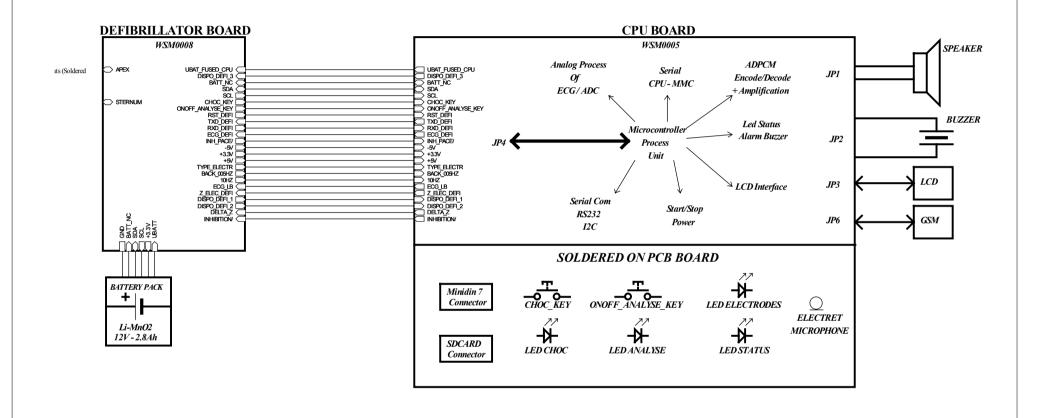

**FRED easy** is technically divided into two subassemblies including:

- The DEFI board includes the various digital processing functions specific to the defibrillator, the analogue processing functions and the high-voltage circuit of the defibrillator.

- The CPU board includes the various functions relating to digital processing, analogue processing, data saving, additional power supplies and controls and displays.

The two boards communicate electrically between each other through a 32-pin connector JP(4).

#### Controls, power supply, display and recording:

The various controls and display elements of the CPU board are as follows:

- An LCD screen that acts as the visual interface between FRED easy and the user.

- A dual-function key (On/Off and Analysis) for controlling device switching on and off. Its other function consists in enabling the starting of a patient signal analysis.

- Two green LEDs indicative of the On/Off Analysis keys offer an additional visual interface for the user.

- The SHOCK key controls the delivering of a defibrillation shock.

- The orange LEDs indicative of the Shock key offer an additional visual interface for the user.

- Status LED that continuously indicates the success of the last device self test

- A buzzer to indicate any anomaly found at the last self test

- An Electrode Fault LED to indicate where the defibrillation electrodes are to be connected. Also

provides information about the continuity of the electrical circuit.

- A speaker for the messages intended for the user.

- A microphone for recording the sound in the environment.

- An MMCard for recording the ECG signal, the events of the operation and the environment sounds.

- A Mini DIN 7 connector for the serial link with a PC in order to download programs and configure FRED easy. During these operations, the board is powered by an external power source through the same connector.

#### Central Process Unit

| Central Process Unit |                  |                       | Schema No.:<br>WSM0005_SYN2 |                                                             |

|----------------------|------------------|-----------------------|-----------------------------|-------------------------------------------------------------|

| Project: 01.58.E.09  |                  | PCB No.: WSW0005_PCB2 | Date: 08/01/03              | Error : Schiller Med.S.A.Logo.bmp i<br>4, rue Louis Pasteur |

| Size: A3             | Drawn by: JME/NF | Art. No.: WSW00054    | Sheet 1 of 9                | ZAE Sud BP50<br>67162 WISSEMBOURG CEDEX                     |

# 5.2 CPU (part no. WSM0005A)

The paragraphs below outline the various functions of the CPU board.

#### General description:

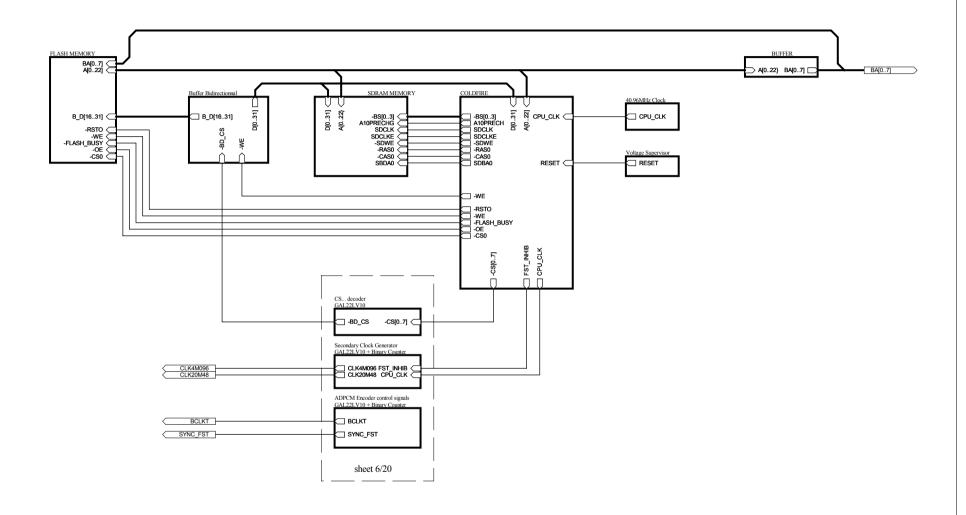

The CPU board includes a ColdFire host microcontroller (U23), the working RAM (U7 and U39) and the flash memory (U37). The ColdFire processor is driven by a 40.96MHz quartz.

The CPU controls the following basic functions:

- Data bus amplification

- Address bus amplification

- Auxiliary power supplies

- Power supply by the Mini DIN 7 connector

- RS232 serial link via the Mini DIN 7 connector

- Configuration EEPROM.

- Communication between the ColdFire microprocessor and the defibrillator

- Starting up of the device when the cell is inserted

- Starting up of the device by the On/Off key

- Start of an analysis

- Delivery of a defibrillation shock

- 3.3 V voltage supervisor

- Time stamping

- Buzzer alarm

- Status LED indicator

- MMcard interface

- CPU hardware configuration

- LCD display interface

- AD converter

- Analogue processing of the ECG signal

- Monitoring of the internal temperature of the device

- Supervision of the power supply cell voltage

- Supervision of the backup cell voltage

- ADPCM decoder for voice message emission

- Audio amplifier for voice message emission

- ADPCM encoder for recording the environment sounds

- · Generation of intermediate clocks

- Recognition of the type of electrode (child/adult)

- EMC measurements

#### Optional functions:

• GSM telephone

Development, debugging and miscellaneous utilities:

- Serial link to list to communication between the ColdFire processor and the defibrillator microcontroller.

- Ethernet link

#### **Data bus amplification:**

The ColdFire data bus has bi-directional amplification through U28. With the exception of DRAM U7 and U39, all the other peripherals use the amplified data bus B\_D(16..31). Signal -WE generated by ColdFire controls the direction of data transmission and signal -BD\_CS generated by programmable circuit U2 of the intermediate clock generation function controls the activation of U28.

#### **Address bus amplification:**

The address bus of the ColdFire processor has unidirectional amplification through U25. Only the eight low addresses A(0..7) are amplified. With the exception of DRAM U7 and U39, all the other peripherals addressed use the amplified address bus BA(0..7).

# Microcontroler Process Unit

| Microcontroler Process unit |                   |                      | Schema No. :<br>WSM0005_SYN2 |        | SCHILLER                             |

|-----------------------------|-------------------|----------------------|------------------------------|--------|--------------------------------------|

| Project: 01                 | .58.E.09          | PCB No.:WSM0005_PCB2 | Date: 08/01/03               |        | MEDICAL S.A.<br>4, rue Louis Pasteur |

| Size: A3                    | Drawn by : JME/NF | Art. No. : WSM0005A  | Sheet                        | 2 of 9 | ZAE Sud BP50                         |

#### **Power supplies:**

#### +3.6 V voltage

The +3.6 V power supply voltage is supplied from the cell voltage by means of chopping regulator U22, chopping transistors U20,U21, free wheel diode D29 and current limiting resistor R220. All these components form a step-down regulator. Voltage control is provided by divider bridge R221 and R222 in parallel with R224. Control by the ColdFire processor of the parallel connection of R224 with R222 increase the 3.6 V voltage during the emission phase of the mobile phone.

#### +3.3 V voltage

The +3.3V voltage is provided from the +3.6 V by dropping the voltage as required in D23.

#### +5 V voltage

The +5 V supply voltage is provided from the cell voltage by means of chopping regulator U29 and free wheel diode D30. The network made up of Q27, D24, D26 and C157 operates like a switching aid, raising the voltage. The components make up a regulator working in the step-down mode. Control is provided by dividing bridge R47, R236.

#### **Backlighting voltage**

The supply voltage of the backlighting is provided from the +5 V voltage through chopping regulator U38. It provides a chopped volume with an approximate amplitude of 190V. The chopping frequency (260Hz) is regulated by R308.

#### -Vee voltage

The -Vee supply voltage is provided from the +5 V by means of chopping regulator U30, chopping transistor Q28, induction coil L8, diode D28 and limiting resistors R241, R242. The current is controlled by R243 in series with R244, in parallel with C151. The assembly makes up a regulator operating in the inverter step-up mode.

#### -5V voltage

The -5 V voltage is provided from -Vee by means of a linear regulator.

#### Power supply by the Mini DIN 7 connector:

The device can be powered by an external power source through the Mini DIN 7 connector that is located in a recess on the internal wall of the lithium cell slot. Access to the connector requires removing the lithium cell. When the power supply is derived from an external power source, signal INHIBITION/ [U27D(11)] switches to low and switches the device to the configuration mode.

The power supply voltage is brought to the various chopping regulators by means of diode D24.

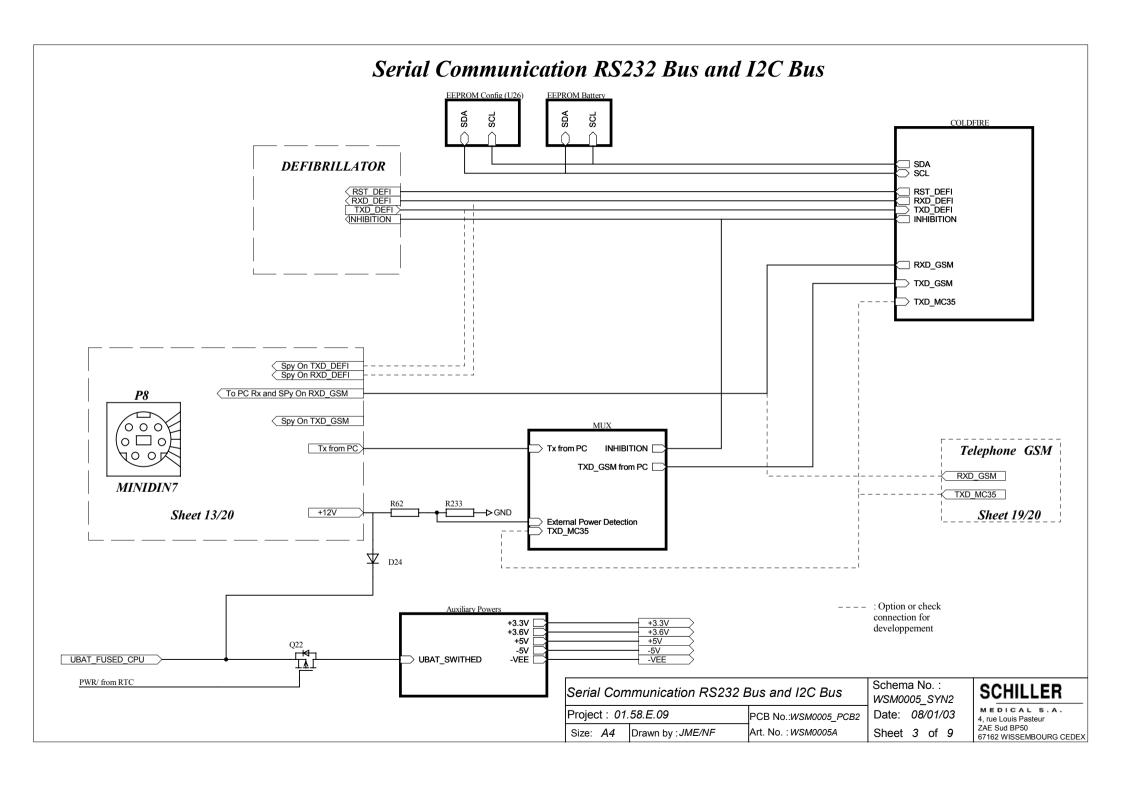

#### RS232 serial link via the Mini DIN 7 connector

The RS232 serial link via the Mini DIN 7 connector (P8) is used chiefly for device program updating and configuration. It takes care of communication between an external PC and the ColdFire processor. It operates at 115.2Kbaud. The use of this serial link means that the device is powered through the Mini DIN 7 connector.

Signal INHIBITION/, output from U27D switches to low when the device is powered by the Mini DIN 7 connector. The Transmit signal generated by the external PC is transmitted to the ColdFire processor through NAND gates U27C and U27A. The Receive signal ending at the external PC is a direct connection. Signal TXD\_GSM is a dual-function line. First of all, it is responsible for communication between the external PC and the ColdFire processor in the configuration mode. Secondly, it takes charge of communication between ColdFire and the (optional) GSM when the device is used for an operation.

All the lines ending in the Mini DIN 7 connector have EMC filters (RC network).

# **Configuration EEPROM**

Configuration EEPROM U26 is under the control of the ColdFire processor through a synchronous serial link. Line SCL carries clock data and the SDA line carries bi-directional data.

#### Communication between the ColdFire microprocessor and the defibrillator

Communication between the ColdFire processor and the defibrillator is provided by a 9600-baud RS232 serial link.

Signal TXD\_DEFI from the defibrillator microcontroller is directly applied to the entry of the ColdFire microprocessor. Signal RXD\_DEFI generated by the ColdFire processor is transmitted to the microcontroller of the defibrillator through a voltage level adaptation stage. The stage is build around Q1 and Q2.

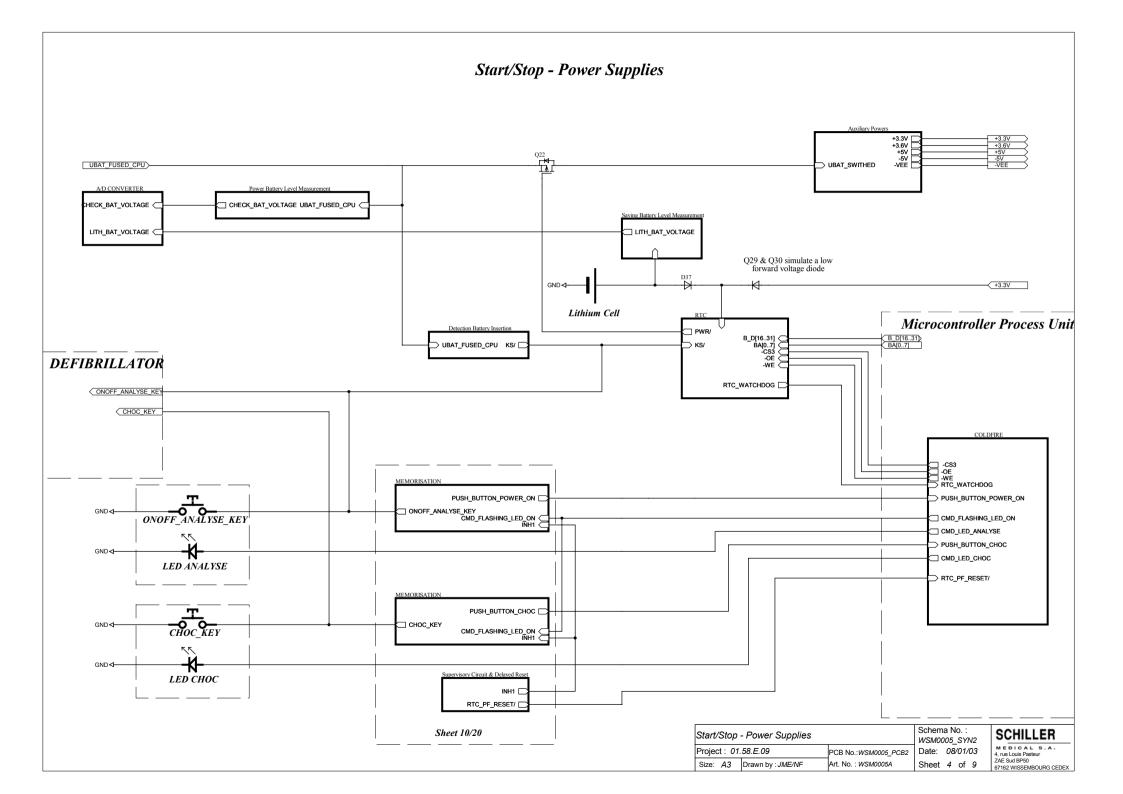

#### Starting up of the device when the cell is inserted:

Inserting the power supply cell starts the device. The device runs a self test and switches off after positioning the Status LED indicator and the buzzer alarm depending on the results of the self test. Inserting the power supply cell generates a pulse at the gate of Q3 through C69, R102, R103 and R104. The pulse is transmitted to input KS/ of the clock. The clock comes out of the standby mode and sets its PWR output to low. That signal makes switching transistor Q22 of the auxiliary power supplies conduct through R121, Q20, R120, Q19 and R123.

#### Notes:

Do not insist for too long if, after the power cell is inserted, the device goes off after three seconds and the message "FRED IS TESTING" has not been displayed on the screen. The depletion of the backup cell is accelerated.

#### Starting and stopping the device with the On/Off key:

The On/Off\_Analysis key has a dual function. It switches the device on and off and makes it possible to start an analysis. The second function has been described in the section "Starting an Analysis".

Pressing key S1 takes input KS/ of clock U9(24) to the ground through D2. That signal saved by latch U11A is transmitted to ColdFire through signal PUSH\_BUTTON\_POWER\_ON. It informs ColdFire of the origin of the starting of the device. Latch U11A is reset by Q6 and signal CMD\_FLASHING\_LED\_ON. It is generated by ColdFire. Signal INH1 keeps transistor Q6 blocked during the rest pulse duration and a few milliseconds after that in order to ensure the saving of signal ONOFF\_ANALYSE\_KEY. That extension of the duration of signal INH1 beyond the reset is achieved by network R367, R368 and C199.

The ONOFF\_ANALYSE\_KEY signal is transmitted and processed by the defibrillator microcontroller. It has no bearing on the working of the defibrillator during the device start-up phase.

The device is stopped by a lengthy press of the On/Off Analysis key.

#### Starting an analysis:

An analysis is started by pressing key S1 when the device is on. The signal is transmitted to the defibrillator microcontroller.

#### Note:

If key S1 is kept pressed for more than three seconds, the device is switched off.

The On/Off\_Analysis key is lit by two green LEDs D20 and D21. The lighting of the LEDs is controlled through transistors Q9 and Q10 and signal CMD\_LED\_ANALYSE generated by ColdFire.

### **Delivering a defibrillation shock:**

A defibrillation shock is delivered by pressing key S2. Pressing key S2 forces signal CHOC\_KEY to zero. That status is saved by latch U11B, the output PUSH\_BUTTON\_CHOC of which switches to high (+3.3 V). The signal is transmitted to the ColdFire microprocessor. Latch U11B is reset through transistor Q6 and signal CMD\_FLASHING\_LED\_ON generated by the ColdFire processor.

#### Note:

Key S2 is only active when it is lit. The Shock key is lit by two green LEDs D18 and D19. The lighting of the LEDs is controlled through transistors Q7 and Q8 and signal CMD\_LED\_CHOC generated by ColdFire.

#### +3.3V power supply voltage supervisor:

The +3.3V power supply voltage is supervised by circuit U10, which gives the reset pulse when the device is started up and supervises the +3.3V power supply voltage when the device is operating. Any drop in voltage below +3V triggers reset pulses.

#### Clock:

Clock U9 is controlled by ColdFire through data bus B\_D(16..31), address bus BA(0..7) and control signals -CS3, -OE and -WE. In addition to its real time clock / calendar function, the clock also wakes the device once a week and provides the PWR/ control signal to start up the device. Entry KS/ of clock U9(24) associated with output PWR/ starts up the device. This function has been described in greater detail in sections "Device starting up upon the insertion of the power cell" and "Starting up and switching off the device with the On/Off key". The clock is driven by quartz Q21 with a speed of 32.768KHz.

#### Note:

The clock accuracy is greater than +/- 30minutes per year.

The clock is powered by the backup cell or by the +3.3 V power supply depending on whether the device is on or off. When the device is off, the clock is powered by the backup cell via D37, R342 and LP1. Transistors Q29 and Q30 are blocked and stop the leakage current flowing to the +3.3 V power. When the device is on, the clock is powered by the +3.3 V supply as the voltage of the collector of Q29 is greater than the voltage of the anode of D37. Current flow from the cell to the clock is blocked.

Signal RTC\_WATCH\_DOG is an interrupt generated regularly by the clock. It may be used by the ColdFire processor to monitor the progress of the program.

#### Note:

The clock also includes a voltage supervisor. This function is not used. Resistor R10 has not been fitted.

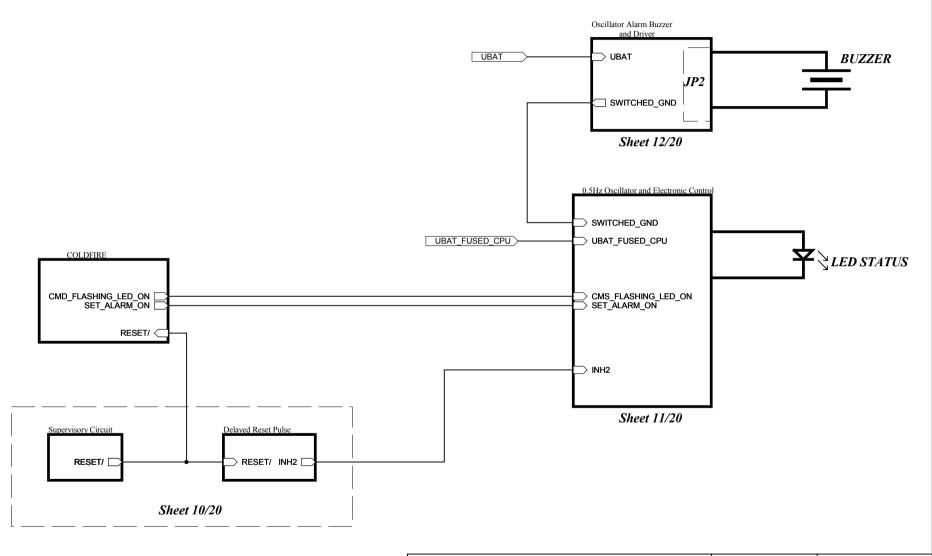

#### **Buzzer Alarm:**

The buzzer alarm is activated when an error is found during the self test phase.

#### Note:

The Buzzer alarm is heard as a sequence of two consecutive beeps that are repeated after every two seconds.

The Buzzer alarm function is powered by UBAT through protection resistors R343 and R344. The buzzer alarm is started up by switching signal SWITCHED\_GND to the ground. That is achieved by transistor Q16 of indicator LED STATUS.

The oscillator built around U17C and U17D generates the attack frequency (? KHz) of the buzzer. The current is amplified by followers U19A to U19F. The buzzer attack signal is modulated by a signal generated by oscillator U17A, U17B and divider U?. The modulation is applied to the oscillator of the buzzer attack frequency through an OR logical gate built around D10, D11 and R137.

#### Note:

Regardless of the starting mode (weekly self test, starting with On/Off key or due to battery insertion), the buzzer alarm starts up as soon as the device is started. It stops after a few seconds if no fault is found during the self test. Otherwise, the buzzer alarm persists till the power cell capacity is depleted.

# **LED STATUS indicator:**

The LED STATUS indicator is a visual indicator that flashes at 0.5Hz. If no error is found, the LED STATUS indicator flashes regardless of the device status – off or on – providing the power cell is in place.

#### Note:

The operating of the LED STATUS indicator is closely linked to that of the buzzer alarm. If the indicator does not flash, the buzzer alarm must start. But the very fact that the LED STATUS indicator does not flash shows a technical fault.

The LED STATUS indicator is powered by UBAT\_FUSED\_CPU. The +5FL auxiliary power supply voltage is provided from the voltage taken from the terminals of C117 through the linear regulator built around U15. It is responsible for the operating of the control of the LED STATUS indicator and the buzzer alarm. The power to supply +5FL to the control circuitry comes from the pulsed current that passes through status LED D22, which is stored via R154 and D7 in C117.

The flashing frequency of indicator LED STATUS is provided by U16. Capacitor C122 fixes the lighting time of indicator LED STATUS and C123 determines its flashing frequency.

Flashing is started by a pulse (~100mS) on line CMD\_FLASHING\_LED\_ON. Output U14B(9) switches to the low logical status. Through Q13, transistor Q23 which shorted status LED D22 switches to the blocked state. The flashing cycle is started. The flashing is maintained by means of D8, Q14 and Q24. The flashing of indicator LED STATUS is stopped and the buzzer alarm is started through signal SET\_ALARM\_ON. A pulse on line SET\_ALARM\_ON forces U14B(9) to the high logical status. Transistor Q23 is saturated and shorts status LED D22, which ceases to flash. At the same time, output 6 of U14A switches to the high status. Transistors Q15 and Q16 saturate and start the buzzer alarm. During the duration of the reset and few dozen milliseconds after that time, signal INH2 keeps transistor Q33 blocked. During that time, the buzzer alarm is blocked.

The binary counter built around U12A, U12B, U13A and U13B introduces a delay when the buzzer alarm is started up. It is 16 seconds.

# Note:

When the device is started up, a buzzer alarm is emitted while the ColdFire processor is booting. Its duration is limited to 16 seconds maximum. During that time, the buzzer alarm does not code for technical faults. The persistence of the buzzer alarm beyond sixteen seconds imperatively indicates a technical fault.

# Status Led Indicator - AlarmBuzzer

Status Led Indicator - AlarmBuzzer

Project : 01.58.E.09

PCB No.:WSM0005\_PCB2

Size: A4

Drawn by : JME/NF

Art. No. : WSM0005A

Schema No. : WSM0005\_SYN2 Date: 08/01/03

Sheet 5 of 9

M E D I C A L S . A .

4, rue Louis Pasteur

ZAE Sud BP50

67162 WISSEMBOURG CEDEX

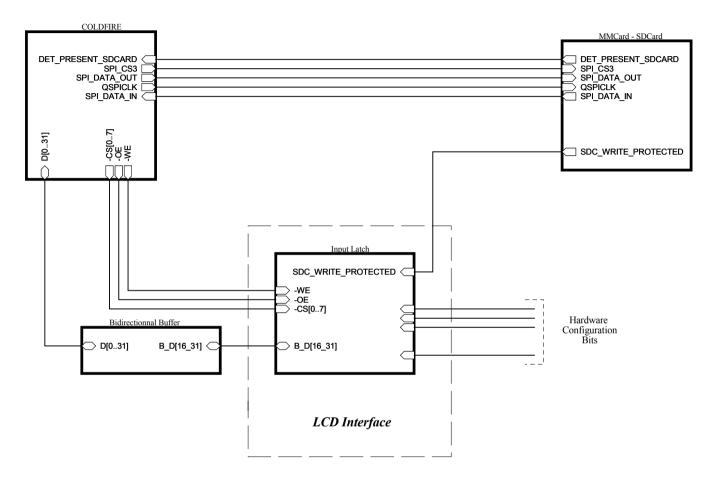

# Multimedia Card (MMcard) interface:

The MMcard interface is made up of a special connector JP5, which is used to receive memory cards of the MMC (Multi Media card) and SDC (Secure Digital Card) type. During use, they are used to record ECG signals, environment sounds and events relating to the procedure.

The MMcard is under the control of the ColdFire processor through signals SPI\_CS3, QSPICLK, SPI\_DATA\_IN and SPI\_DATA\_OUT.

Signals DET\_PRESENT\_SDCARD and SDC\_WRITE\_PROTECTED are status signals of the memory card, which indicate the presence and write-protection of the MMcard respectively. The signals are active in the low logical state. The lines connected with JP5 are all protected by resistors of 22.1  $\Omega$ . The power supply of the MMcard is protected by fuse F2.

# **CPU** hardware configuration:

The hardware configuration is performed through the input latch U41. The first seven inputs of the latch can be forced to a low or high logical status that depends on the installation of appropriate resistors.

#### Note:

The eighth input is occupied by signal SDC\_WRITE\_PROTECTED and cannot be used for hardware configuration.

Input latch U41 is under the control of ColdFire through data bus B\_D(24..31) and signals -CS1 and -OE via gate OR of U40A. Control signal LCD\_ENAB (input 11 of U41) is generated by latch U42 (see section AFFICHAGE\_LCD).

# Serial Communication between CPU and MMC

| Serial Communication between CPU and MM |                   | CPU and MMC                | Schem |     |      | <b>/</b> 2 | 1 |

|-----------------------------------------|-------------------|----------------------------|-------|-----|------|------------|---|

| Project : 01.58.E.09                    |                   | PCB No.:WSM0005_PCB2       | Date: | 08/ | 01/0 | 03         | 4 |

| Size: A4                                | Drawn by : JME/NF | Art. No. : <i>WSM0005A</i> | Sheet | 6   | of   | 10         | Z |

SCHILLER

MEDICAL S.A.

4, rue Louis Pasteur

ZAE Sud BP50

67162 WISSEMBOURG CEDEX

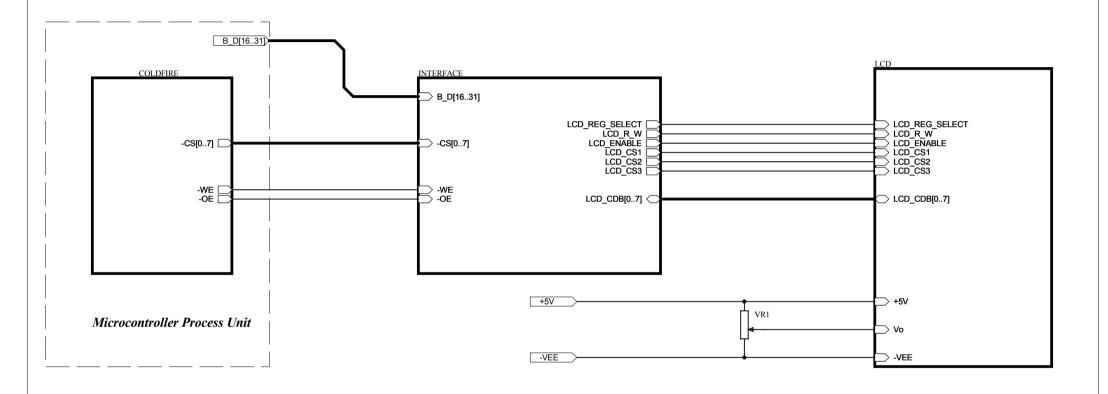

# LCD display:

The LCD display is under the control of the ColdFire processor through data bus B\_D[24..31]. The LCD registers are written through latch U43. It is controlled by signal LCD\_R\_W generated by latch U42 and through an OR gate, by signals -WE and -CS4 of the ColdFire processor.

The LCD registers are re-read through latch U44, which is controlled by signal LCD\_ENAB generated by latch U42, through an OR gate, by signals -OE and -CS4 of ColdFire.

The various control signals (LCD\_CS1, LCD\_CS2, LCD\_CS3, LCD\_REG\_SELECT, LCD R\_W and LCD\_ENAB) are provided from the data bus through latch U42. It is controlled through an OR gate by signals -WE and -CS1 of the ColdFire processor.

The screen is powered with +5 V, via R114 and R277 and -VEE, via R275 and R276. The contrast is adjusted by means of VR1. The nominal contrast adjustment is around —8 V. All links with the LCD screen are filtered by RC networks.

# LCD Interface

| LCD Interface |              | ace               |                      | Schema No. : WSM0005_SY |    |      |     |

|---------------|--------------|-------------------|----------------------|-------------------------|----|------|-----|

|               | Project: 01. | .58.E.09          | PCB No.:WSM0005_PCB2 | Date:                   | 09 | /01/ | ′0З |

|               | Size: A4     | Drawn by : JME/NF | Art. No. : WSM0005A  | Sheet                   | 7  | of   | 9   |

Schema No. :

WSM0005\_SYN2

Date: 09/01/03

SCHILLER

MEDICAL S.A.

4, rue Louis Pasteur

4, rue Louis Pasteur

ZAE Sud BP50

67162 WISSEMBOURG CEDEX

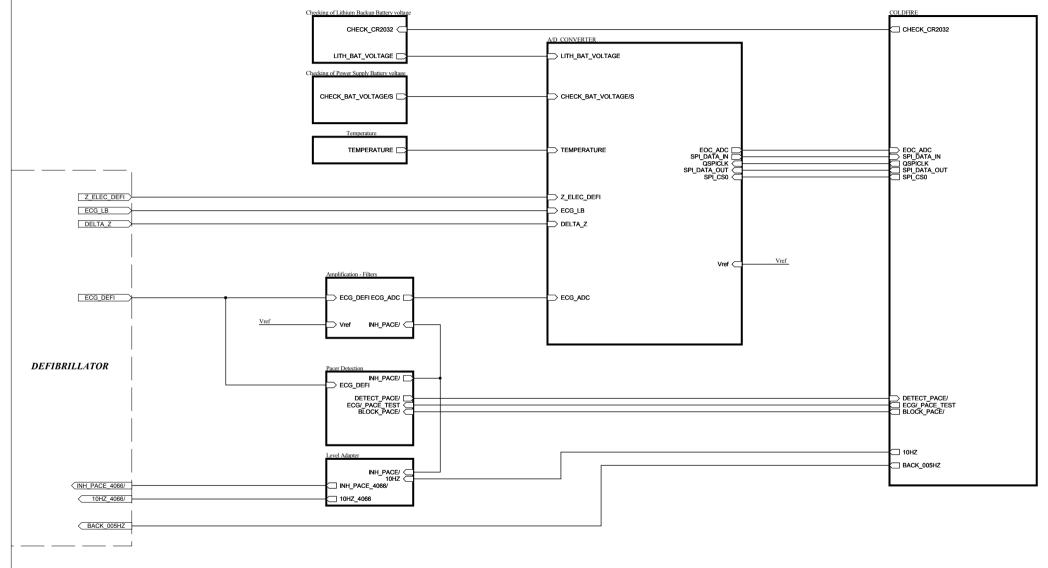

# **AD** converter:

The AD converter (U35) is under the control of the ColdFire processor through an SPI serial link (QSPICLK, SPICSO, SPI\_DATA\_OUT and SPI\_DATA\_IN). Line EOC (end of convert) is a converter status signal that informs the ColdFire processor of the end of conversion and the availability of the converted data. The converter resolution is 10 bits and its voltage reference (2.5 V) is supplied by D36

The AD converter has eight multiplex analogue inputs that enable it to digitise the following signals:

- Z ELEC DEFI: analogue signal from the defibrillator. Carries patient impedance information. Before being applied to the converter, signal Z\_ELEC\_DEFI is divided by two with resistors R351 and R352. The signal is filtered from the EMC point of view at the input of the CPU board by a T filter made up of R186, C134 and R194.

- <u>ECG LB:</u> analogue signal from the defibrillator. Carries ECG information with a narrow bandwidth (0.05Hz 1Hz). The signal is filtered from the EMC point of view at the input of the CPU board by a T filter made up of R185, C135 and R193.

- <u>ECG\_ADC</u>: analogue signal from the defibrillator. Carries ECG information with a wide bandwidth (1Hz - 25Hz). Before it is applied to the input of the ADC, signal ECG\_ADC is conditioned by the analogue processing function of the CPU board. The signal is filtered from the EMC point of view at the input of the CPU board by a filter made up of C34 and R200.

- <u>CHEK BAT VOLTAGE/5</u>: Analogue signal. Carries information about the power cell voltage. The signal is taken from UBAT\_FUSED\_CPU through the divider bridge made up of R105 and R127. When the device is switched off, transistor Q4 in series with the divider bridge prevents the current from flowing to the ground. As a result, the gate source voltage of Q31 is zero and the leakage of current to the ADC input is interrupted.

- <u>DELTA Z:</u> analogue signal from the defibrillator. Carries information about the impedance variation used for movement detection. The signal is filtered from the EMC point of view at the input of the CPU board by a T filter made up of R204, C132 and R197.

- <u>TEMPERATURE</u>: probe U36 provides analogue voltage proportional to the internal temperature of the device. It is directly applied to the input of the CAD.

- <u>LITH\_BAT\_VOLTAGE</u>: This signal carries information about the voltage of the backup cell.

The link between the ADC input and the backup cell is provided through transistor Q34 which is controlled by signal CHEK\_CR2032. The control prevents the leakage of current to the ADC input.

## **Analogue processing of the ECG signal:**

Analogue processing of the ECG\_DEFI signal consists of finally filtering, amplifying and offsetting the direct component before it is digitised and special filtering for extracting the PACE information.

Signal ECG\_DEFI is applied to analogue switch U45, which is responsible for opening the amplification circuit when a stimulation pulse is detected. The opening is commanded by signal INHIB\_PACE/.

At the output of the switch, the signal is applied to follower U46 through a capacitive link made up of R33 and C53, the role of which is to eliminate the continuous component of signal ECG\_DEFI. Final amplification and filtering is performed by U32C. Through the divider bridge made up of R86, R223 and R245, circuit U32C brings the dynamics of signal ECG\_ADC to the middle of the ADC conversion range.

The PACE information is extracted from signal ECG\_DEFI through the amplification and filtering circuit built around U32A, U32C and U32D. The output of the amplification and filtering circuit is applied to comparators U34A and U34B, which control the triggering of monostable U33A and U33B. At the monostable output, D14, D15 and R66 form an AND gate, through which stimulation pulse recognition DETECT\_PACE/ is transmitted to ColdFire. In response, the ColdFire processor sends a low logical status of a set duration on line BLOCK\_PACE/.

# **Internal device temperature monitoring:**

Temperature probe U36 provides analogue voltage proportional to the internal temperature of the device. It is directly applied to the input of the CAD.

#### Note:

The measurement is used to optimise the use of the power cell.

# Power cell voltage monitoring:

The power cell voltage is taken from UBAT\_FUSED\_CPU through dividing bridge R105 and R127. The resulting signal CHEK\_BAT\_VOLTAGE/5 is transmitted to the ADC. The role of transistors Q4 and Q31 is to prevent leakage current from flowing to the ground and in the input of the CAD when the device is off (no + 3.3V).

# Backup cell voltage monitoring:

The voltage of backup cell V\_LITH is taken at the anode of D37 and transmitted through transistor Q34 to ADC converter U35. The role of the function built around Q34 and Q35 is to prevent leakage current from flowing to the ADC input when the device is switched off. Signal CHECK\_CR2032 generated by ColdFire controls the connection between the backup cell and the ADC input.

# Analog Processing of ECG - A/D conversion

| Analog Processing of ECG - A/D |        | cessing of ECG - A/L |                   | oversion Schema WSM000 |       |      |      |    |

|--------------------------------|--------|----------------------|-------------------|------------------------|-------|------|------|----|

|                                | Projec | ct: 01.              | 58.E.09           | PCB No.: WSM0005_PCB2  | Date: | 09/0 | 01/0 | )3 |

|                                | Size:  | A3                   | Drawn by : JME/NF | Art. No. : WSM0005A    | Sheet | 8 (  | of   | 9  |

Perma No. :

M0005\_SYN2

e: 09/01/03

et 8 of 9

SCHILLER

MEDICAL S.A.

4, rue Louis Pasteur

ZAE Sud BP50

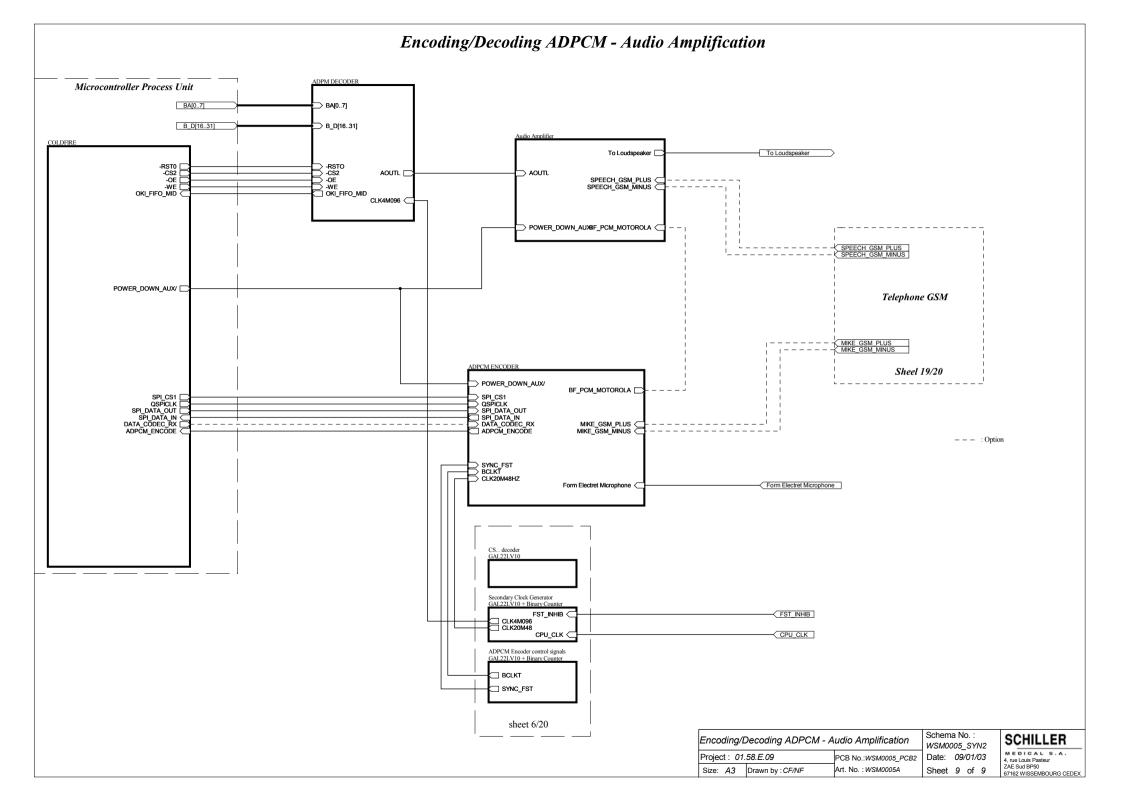

#### ADPCM decoder:

The ADPCM decoder is controlled by the ColdFire processor through data bus B\_D[16..31] and control and status signals -CS2, -OE, -WE, BA0, -RST0 and OKI\_FIFO\_MID. The operating frequency of the decoder is 4.096MHz. It is provided by the intermediate clock generation function that is built around U2. The ADPCM decoder issues an analogue output on its output AOUTL [UU4(28)]. The signal is applied to an audio amplifier through capacitive connection C104.

#### Audio amplification:

The audio amplifier is built around circuit U5. The three signals to be amplified come from the ADPCM decoder (output 28 of U4), the ADPCM encoder (BF\_PCM\_MOTOROLA) and the GSM option (SPEECH\_GSM\_PLUS) and are brought to the audio amplifier via a capacity connection mixer built around U6A. Through a capacitive link (C62) that also takes care of high pass filtering, the audio signal is pre-amplified and undergoes low pass filtering thanks to the function built around U6B. After that, the audio signal is applied via a capacitive link (C106) to the input of the power amplifier, the output of which attacks the speaker. Power amplifier U5 can be put into standby mode with the help of signal POWER\_DOWN\_AUX/.

#### ADPCM encoder:

The ADPCM encoder is responsible for digitally compressing analogue signals taken via an electret microphone. The electret microphone is polarised from the +5 V through R92 and R93. The signal delivered by the microphone is transmitted to the encoder through the capacitive link made up of C45 and C46. Resistors R98, R99, R100 and R101 form the gain at the analogue input stage of the encoder.

The ADPCM encoder is controlled by ColdFire through a serial SPI link with the help of signals SPI\_CS1, QSPICLK, SPI\_DATA\_IN, SPI\_DATA\_OUT and reset signal POWER\_DOWN\_AUX/. The basic frequency of the encoder is 20.48MHz. The data transmission baud rate is supplied by signal BCLKT. The frame synchronisation frequency is given by signal SYNC\_FST. It is 8KHz. All these frequencies are provided by the intermediate clock generation function that is built around U2. The encoded data are transmitted to the ColdFire processor through signal ADPCM\_ENCODE. Signals DATA\_CODEC\_RX and BF\_PCM\_MOTOROLA are part of the decoder function of MC145540, which is not currently used.

# **Intermediate clock generation:**

Intermediate clocks CLK\_20M48HZ and CLK4M096 and synchronisation signals BCLKT and SYNC\_FST are chiefly used by the ADPCM encoder and decoder. All these signals are generated from clock CPU\_CLK (40.96MHz). Intermediate clock generation is achieved by the binary counters of programmable circuit U2. Asynchronous counter U3 is essentially used to prepare synchronisation signals BCLKT and SYNC\_FST.

# Recognition of the type of electrode:

The type of electrode used – child or adult – is recognised by a reed type contact REL1. The child electrode connector has a magnet that draws contact REL1 and forces signal TYPE\_ELECTR to the low logical status. The signal is transmitted to the defibrillator microcontroller.

#### Note:

The adult electrode connector does not have a permanent magnet.

#### **EMC** measurements:

The CPU circuitry is enclosed in a metal housing that is connected at several locations to the CAVE ground plane that acts as the reference for EMC filtering. The CAVE ground plane occupies the outer layer of the CPU board and therefore forms an enclosure with the metal housing. All the input and output CPU signals are filtered by networks RC and LC.

#### **GSM** interface:

The GSM interface is optional. The link between the CPU and the GSM interface is provided by a flat jumper via connector JP6.

The GSM interface is controlled by the ColdFire processor through the serial link RXD\_GSM, TXD\_MC35 and signal GSM\_IGNITION. It is powered with +3.6 V via L9. Signal SYNC\_POWER\_BURST acts on voltage +3.6 V, which is slightly raised during the GSM emission phase.

Audio signals SPEECH\_GSM\_PLUS and SPEECH\_GSM\_MINUS are amplified by the audio amplifier and rendered by the device speaker.

Lines MIKE\_GSM\_PLUS and MIKE\_GSM\_MINUS are those of the audio signal recorded by electret microphone MK1. Connector P2 is used for the GSM SIMM card.

# **Description of labels and port modules:**

| A[022] ColdFire address bus Encoded ADPCM data transmitted to ColdFire.  A10 PRECHG SDRAM control signal.  BA[07] Amplified address bus ECG_LB signal trace retrieval command after a defibrillation shock. Active when high.  Not used.  BATT_NC Not used.  BD_CS Data bus buffer control signal.  BDM_CPU_CLK Signal of port BDM and JTAG. Not involved in device operation. Audio output of ADPCM encoder. Not used.  BS[03] Signal of port BDM and JTAG. Not involved in device operation. Control signal of port BDM and JTAG. Not involved in device operation. Audio output of ADPCM encoder. Not used.  Signal of port BDM and JTAG. Not involved in device operation. Control signal of port BDM and JTAG. Not involved in device operation. Audio output of ADPCM encoder. Not used.  Signal of port BDM and JTAG. Not involved in device operation. Control signal of the analogue switch of the amplification chair to suppress the pacing pulse. Active when low.  Control signal of data transfer between the SDRAM and ColdFire.  CHEK_BAT_VOLTAGE/5 CHEK_CR2032  CHEK_BAT_VOLTAGE/5 CHEK_CR2032  CHOC_KEY  CLX4M096  CLX20M48HZ  CMD_LED_ANALYSE  CMD_LED_ANALYSE  CMD_LED_ANALYSE  CMD_LED_CHOC  CMD_LED_ANALYSE  CMD_LED_CHOC      |                                      |                 |                           |